Master-Arbeiten

Betreuer*in: Christian Hochberger

Frühester Beginn: sofort

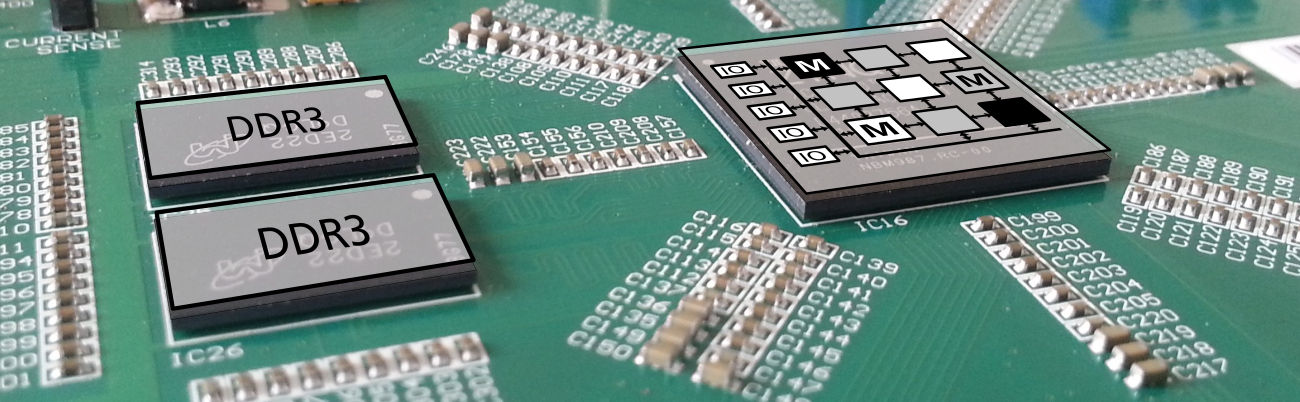

Coarse Grained Reconfigurable Arrays (CGRA) sind hochparallele Rechenstrukturen, die eine sehr große Rechenleistung bereitstellen können. Häufig werden sie in Prozessor-basierte Systeme als Beschleuniger integriert. Dann werden rechenintensive Teile der Anwendung vom Prozessor an das CGRA delegiert.

Die Programmierung des CGRA erfolgt mit Hilfe eines sehr speziellen Schedulers, der den Binärcode für das CGRA generiert. Das Format der Eingangsdaten für den Scheduler ist eine spezialisierte Graph-Struktur (SCAR = Scheduler Application Representation).

In einigen Anwendungen ist es nützlich, wenn das CGRA stand-alone betrieben werden kann. In diesen Fällen soll seine Programmierung mit regulärem C-Code erfolgen.

Das existierende Tool für die Abbildung von C-Code auf SCAR-Graphen hat eine Reihe von Schwächen und beherrscht nicht alle Programmstrukturen, die gebraucht werden. Ziel dieser Arbeit ist es, ein neues Tool für die Abbildung von C-Code auf SCAR-Graphen zu entwickeln. Als Basis für dieses neue Tool kommen verschiedene Frameworks in Frage: Cetus, LLVM oder auch GCC.

Es bietet sich an, die Masterarbeit mit einem vorangestellten Projektseminar zu verbinden.

Generelle Hinweise

Es werden grundsätzluch keine Arbeiten angeboten, für Kenntnisse in der Programmiersprache Python ausreichende Programmierkenntnisse darstellen.

Wenn Sie eines der Themen interessiert, es sich aber um die falsche Art der Arbeit handelt, können Sie trotzdem Kontakt mit dem/der Betreuer/in aufnehmen. Möglicherweise kann die Arbeit Ihren Bedürfnissen angepasst werden oder es findet sich ein ähnliches Thema.

Die hier aufgeführten Bachelor-Projektseminare werden nur an Studierende vergeben, die nicht Datentechnik (B.Sc. ETiT) vertiefen. Projektseminare werden häufig in einem ähnlichen Themenbereich wie die anschließende Bachelor-Arbeit absolviert. Daher können Sie bei der Suche nach einem Projektseminar auch nach den Themen für Bachelor-Arbeiten schauen.