Bachelor-Arbeiten

Betreuer*in: Leon Mayrhofer

Frühester Beginn: sofort

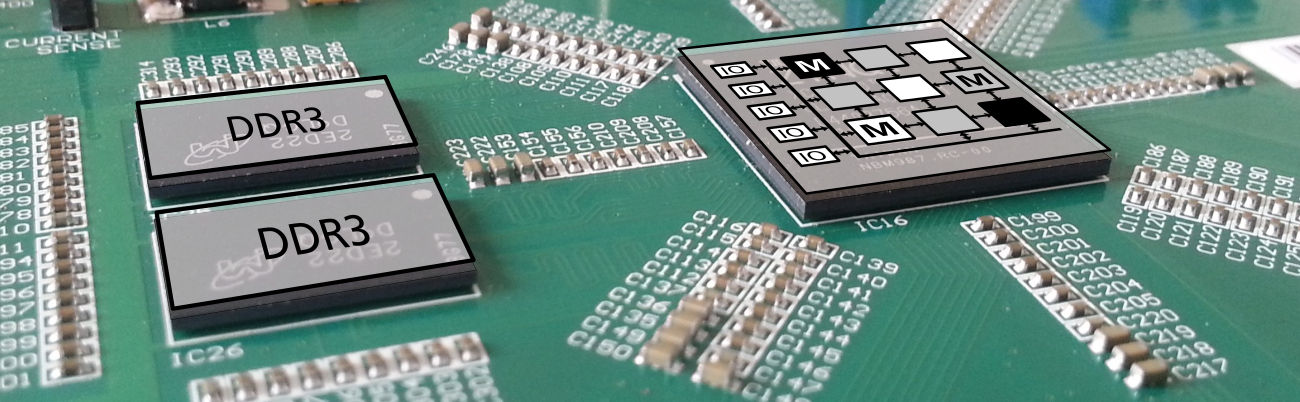

Das Fachgebiet Rechnersysteme betreibt das SpartanMC SoC-Kit, welches für den Einsatz auf FPGAs optimiert wurde. Ein Bestandteil des SoC-Kits ist der Peripherie-Bus und die dazugehörige umfangreiche Sammlung an Peripherie-Komponenten. Mit Hilfe von jConfig ist das automatisierte Erstellen von quasi arbiträren Kombinationen aus Peripherie-Komponenten in Verbindung mit SpartanMC soft-cores möglich. Neben den HDL Beschreibungen der Peripheriemodule werden unter anderem auch Hilfsdateien für die Compiler-Toolchain des SpartanMC erstellt.

Seit einiger Zeit wird parallel zu dem SpartanMC auch ein eigener RISC-V Kern in Chisel entwickelt. Dieser befindet sich aktuell jedoch in einem deutlich weniger ausgereiften Stadium. So gibt es für diesen Prozessor unter anderem noch keine Möglichkeit, Peripherie automatisiert und standardisiert zu erzeugen und in den Toolflow zu inkludieren.

Ziel dieser Arbeit ist es, eine Analyse des SpartanMC Peripheriesystems durchzuführen. Hierbei soll zuerst festgestellt werden, ob jConfig so angepasst werden kann, dass damit auch Konfigurationen für RISC-V Prozessoren inklusive der benötigten Hilfsdateien erstellt werden können. Außerdem soll eine Performance Analyse der einzelnen Peripherie-Komponenten durchgeführt werden. Dabei geht es vor allem um die maximal erreichbare Taktfrequenz.

Basierend auf den Erkenntnissen aus den zuvor ausgeführten Analysen soll ein Peripheriesystem für den RISC-V Prozessor erstellt werden. Dieses soll den maximal erreichbaren Takt des RISC-V Kerns nicht beeinflussen.

Projektseminare Master

Betreuer*in: Christoph Flothow

Frühester Beginn: sofort

Das Technology Mapping ist ein wichtiger Schritt in der Logiksynthese, in der die gewünschte Funktionalität der Schaltung, als Boolesche Funktionen beschrieben, auf Elemente der Zieltechnologie abgebildet wird. Bei FPGAs handelt es sich hierbei um Lookup Tables (LUTs). Die Güte dieser Abbildung kann sowohl Auswirkungen auf die erreichbare Taktfrequenz, als auch auf die Anzahl der LUTs und somit auf die Größe des benötigten FPGAs haben.

Ein gängiges Verfahren in diesem Bereich ist der sogenannte Priority Cuts Algorithmus, der in dem open source Tool ABC implementiert ist. Hier werden Cuts in einem And-Inverter Graph (AIG) so gesetzt, dass die gesamte Logik, die in einem Cut enthalten ist, direkt auf eine einzelne LUT abgebildet werden kann. Diese Cuts sind in ihrer Größe stark begrenzt, da die Anzahl an Eingangssignalen limitiert ist auf die Anzahl der Eingänge einer einzelnen LUT. Eine Erweiterung dieses Verfahrens hat erreicht, dass etwas größere Cuts im Laufe des Mappings mit einbezogen werden konnten, in dem diese später weiter dekomponiert werden. Dies führte dann zu besseren Ergebnissen in Bezug auf die Tiefe des Mappings.

Der aktuelle Algorithmus ist auf Cuts mit einer Größe von maximal 11 Eingängen begrenzt. Es wird vermutet, dass die Nutzung von größeren Cuts hier zu einer Verbesserung der Ergebnissen führen könnte. Ziel dieser Arbeit ist es, zu analysieren wie häufig es vorkommt, dass mit größeren Cuts eine sogenante "Composition Funktion" gefunden werden kann, die mit einer LUT mit 6 Eingängen realisiert werden kann. Je nachdem, welche Erkenntnisse aus dieser Analyse gewonnen werden, wäre es möglich eine Abschlussarbeit anzuschließen, wo die tatsächliche Erweiterung des Algorithmus vorgenommen wird.

Generelle Hinweise

Es werden grundsätzlich keine Arbeiten angeboten, für die ausschließlich Kenntnisse in der Programmiersprache Python eine ausreichende Grundlage an Programmiererfahrung darstellen.

Wenn Sie eines der Themen interessiert, es sich aber um die falsche Art der Arbeit handelt, können Sie trotzdem Kontakt mit dem/der Betreuer/in aufnehmen. Möglicherweise kann die Arbeit Ihren Bedürfnissen angepasst werden oder es findet sich ein ähnliches Thema.

Die hier aufgeführten Bachelor-Projektseminare werden nur an Studierende vergeben, die nicht Datentechnik (B.Sc. ETiT) vertiefen. Projektseminare werden häufig in einem ähnlichen Themenbereich wie die anschließende Bachelor-Arbeit absolviert. Daher können Sie bei der Suche nach einem Projektseminar auch nach den Themen für Bachelor-Arbeiten schauen.