M.Sc. Christoph Flothow

Lehrveranstaltungen

Forschungsthemen

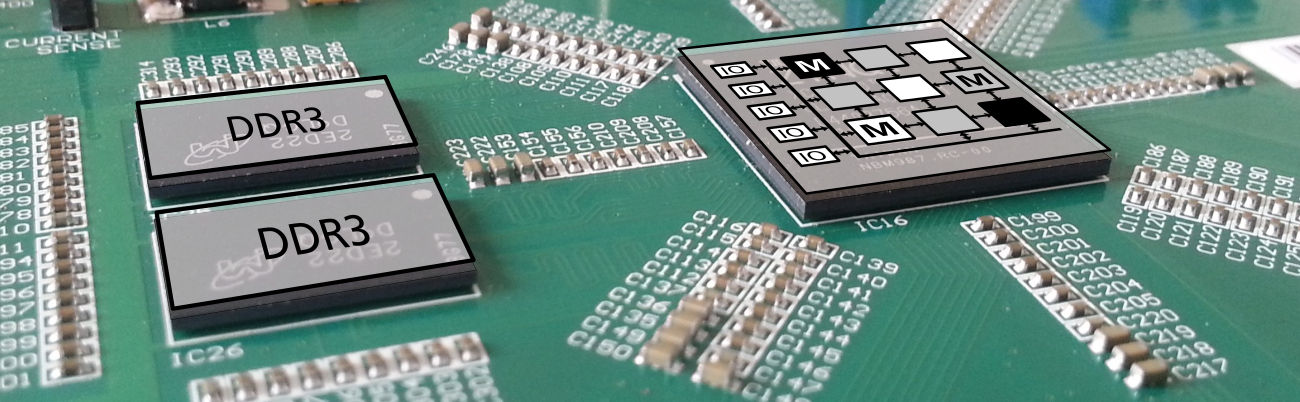

- Technology Mapping für FPGAs

Offene Arbeiten

Leider sind im Moment keine konkreten Themen verfügbar. Falls Sie auf der Suche nach einer Arbeit sind, können Sie sich dennoch gerne an uns wenden. Am besten geben Sie dabei den Bereich an, der Sie besonders interessiert. Dann können wir versuchen, ein geeignetes Thema zu finden.