Bachelor-Arbeiten

Student*in: Laurenz Lemke

Betreuer*in: David Scheunert

Zeitraum: 16.12.2024 - 16.06.2025

Im Bereich der Entwicklung von Steuergeräten und eingebetteten Systemen hat sich seit einigen Jahren die Methodik "Hardware-in-the-loop" etabliert. Dabei wird ein Steuergerät nicht mit dem realen System verbunden, welches es kontrollieren soll, sondern mit einer Simulation dieses Systems. Diese Methodik lässt sich auch auf komplexe Regelungssysteme im wissenschaftlichen Bereich übertragen. So ist es denkbar, die Strahlregelung eines Cyclotrons nicht am realen Cyclotron auszutesten und zu entwickeln, sondern stattdessen ein Modell eines Strahls zu rechnen und somit die Strahlreaktion auf die Regelungseingriffe nur zu simulieren.

Am Fachgebiet Rechnersysteme wird seit mehreren Jahren an Coarse Grained Reconfigurable Arrays (CGRA) als Rechenbeschleuniger geforscht. Dabei wurde in einem vorhergehenden Projekt auch schon ein physikalisches Modell in einem industriellen Umfeld in Echtzeit simuliert. CGRAs haben also bereits bewiesen, dass sie für den Einsatz in Echtzeitsystemen gut geeignet sind. Es bietet sich daher an, die Strahlsimulation ebenfalls mithilfe von CGRAs zu realisieren. Dies wurde im Rahmen einer vorhergehenden Arbeit umgesetzt und die Implementation am realen Strahlregelungssystem getestet.

Im Rahmen dieser Bachelorarbeit sollen die Sensorzugriffsmöglichkeiten des CGRAs erweitert werden. Dazu soll zunächst ein Filter für die Eingangssignale entwickelt werden, um Rauschen auf diesen Signalen zu reduzieren. Anschließend soll das CGRA so erweitert werden, dass es zusätzlich zu Ganzzahlen auch Fließkommazahlen einlesen kann. Abschließend soll die Anzahl der Sensorports des CGRAs erhöht werden und eine spezielle Leseoperation ergänzt werden, die automatisch in Hardware eine lineare Interpolation zwischen zwei Messwerten durchführt.

Master-Arbeiten

Student*in: Danya Rivaldi

Betreuer*in: David Scheunert

Zeitraum: 22.07.2024 - 20.01.2025

Coarse Grained Reconfigurable Arrays (CGRA) sind hochparallele Rechenstrukturen, die eine sehr große Rechenleistung bereitstellen können. Häufig werden sie in Prozessor-basierte Systeme als Beschleuniger integriert. Dann werden rechenintensive Teile der Anwendung vom Prozessor an das CGRA delegiert.

Die Programmierung des CGRA erfolgt mit Hilfe eines sehr speziellen Schedulers, der den Binärcode für das CGRA generiert. Das Format der Eingangsdaten für den Scheduler ist eine spezialisierte Graph-Struktur (SCAR = Scheduler Application Representation).

In einigen Anwendungen ist es nützlich, wenn das CGRA stand-alone betrieben werden kann. In diesen Fällen soll seine Programmierung mit regulärem C-Code erfolgen.

Das existierende Tool für die Abbildung von C-Code auf SCAR-Graphen hat eine Reihe von Schwächen und beherrscht nicht alle Programmstrukturen, die gebraucht werden. Ziel dieser Arbeit ist es, ein neues Tool für die Abbildung von C-Code auf SCAR-Graphen zu entwickeln. Als Basis für dieses neue Tool kommen verschiedene Frameworks in Frage: Cetus, LLVM oder auch GCC.

Es bietet sich an, die Masterarbeit mit einem vorangestellten Projektseminar zu verbinden.

Student*in: Katharina Schultheis

Betreuer*in: Christoph Flothow

Zeitraum: 25.04.2024 - 20.02.2025

In FPGAs werden zur Speicherung der Konfigurationsdaten typischerweise SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind elektronische Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen defektbehaftet ist. Eine einzige defekte Speicherzelle mit undefiniertem Zustand führt dazu, dass klassische Look-up-Tables (LUTs) nur noch zur Hälfte nutzbar sind. Beim Entwurf von Logik-Elementen für NV-FPGAs müssen potentielle Defekte und ihre Auswirkungen also im Sinne einer besseren Defekttoleranz berücksichtigt werden.

Das Ziel dieser Masterarbeit ist der Entwurf eines alternativen Logikelements für NV-FPGAs. Die Entwurfsparameter des Elements sollen im Rahmen einer ausführlichen Design Space Exploration ermittelt werden. Diese soll auf einem aussagekräftigen Satz von Schaltungsentwürfen beruhen. Als Zielfunktionen der Optimierung sind sowohl der Hardware-Bedarf, die Verzögerungszeit, als auch die Defekttoleranz zu berücksichtigen.

Student*in: Yuan Zhao

Betreuer*in: Leon Mayrhofer

Zeitraum: 03.03.2025 - 01.09.2025

Am Fachgebiet Rechnersysteme wird ein RISC-V Soft-Core in Chisel portiert. Dieser dient vorwiegend für die Verwendung in FPGAs. Aufgrund dieser Zielausrichtung bietet es sich an, einen Soft-Core-Generator zu implementieren, mit dem der RISC-V Prozessor an die anwendungsspezifischen Anforderungen angepasst werden kann.

Bisher ist der RISC-V Soft-Core in einer sehr einfachen Basisvariante implementiert. Erweiterte Funktionen wie beispielsweise eine Floating-Point-Recheneinheit sind nicht vorhanden. Die Aufgabe in dieser Master-Arbeit besteht darin, die vorhandene Implementierung um eben solche fortgeschrittenen Funktionen zu erweitern.

Der Aspekt des Generierens von verschiedenen Ausbaustufen des RISC-V Soft-Cores kann durchaus elegant durch den Einsatz der Chisel HDL erreicht werden. Chisel arbeitet auf einer höheren Abstraktionsebene als zum Beispiel Verilog oder VHDL und erlaubt es mit sehr wenig Aufwand einfach zu konfigurierende generische Module zu erstellen. Da das bereits vorhandene System in Chisel vorliegt, ist der Einsatz von Chisel bei dieser Arbeit verpflichtend. Es werden allerdings auch Verilog-Kenntnisse vorausgesetzt, da Chisel-Code vor der Synthese zu Verilog konvertiert wird.

Student*in: Mohamed Saleh

Betreuer*in: Leon Mayrhofer

Zeitraum: 15.05.2025 - 12.11.2025

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Um bei Änderung des Programms nicht eine volle Synthese zur Änderung des Speicherinhaltes durchführen zu müssen, wurde für das SpartanMC SoC-Kit eine Library entwickelt, die auch einen nachträglichen Ausstausch von Speicherinhalten im fertigen Bitstream in Sekunden ermöglicht. Da dieser Austausch nicht für alle Konstellationen aus FPGA und Speicherstruktur funktioniert, soll das Tool FPGoAt entwickelt werden.

Aufbauend auf den Ergebnissen des vorangegangenen Projektseminars soll im Rahmen dieser Master-Arbeit das neue Tool FPGoAt entstehen, um die nachträgliche Aktualisierung von beliebigen Speicherinhalten zu ermöglichen. Ein Teil der Arbeit wird die Entwicklung eines Graphical-User-Interface (GUI) sein, mit dem das Backend von FPGoAt benutzerfreundlich bedient werden kann.

Student*in: Julian Veit

Betreuer*in: David Scheunert

Zeitraum: 23.12.2024 - 23.06.2025

Die Kommunikation zwischen Drohnen spielt eine immer bedeutendere Rolle, insbesondere im Kontext von Schwarmtechnologien, bei denen mehrere Drohnen zusammenarbeiten, um komplexe Aufgaben zu bewältigen. Eine effiziente und zuverlässige Kommunikation ist entscheidend, um Informationen in Echtzeit auszutauschen und eine koordinierte Steuerung des Schwarms zu ermöglichen. Dies betrifft vor allem sicherheitsrelevante Aspekte wie die Vermeidung von Kollisionen und die Optimierung von Flugbahnen.

In dieser Arbeit soll ein Erweiterungsboard auf Basis eines Field Programmable Gate Arrays (FPGA) für die Crazyflie-Drohnen programmiert werden, das in einem vorherigen Projektseminar entwickelt und hergestellt wurde. FPGAs bieten dabei durch ihre Parallelverarbeitungsfähigkeit die ideale Grundlage, um tiefe neuronale Netze für die Low-Level-Steuerung von Drohnen zu implementieren.

Neben der Bereitstellung zusätzlicher Rechenleistung integriert das Board auch eine WiFi-Schnittstelle mit Hilfe eines ESP32, um die Kommunikation zwischen den Drohnen zu verbessern.

Ziel dieser Masterarbeit ist es, die Kommunikation der Drohnen mittels der neuen WiFi-Schnittstelle einzurichten und zu evaluieren. Außerdem soll ein neuronales Netz mit Hilfe von High-Level-Synthese auf dem Board implementiert werden. Anschließend soll die Funktionsfähigkeit des gesamten System experimentell mit mindestens drei Drohnen validiert werden.

Projektseminare Bachelor

Student*in: Nikolai Shauchenka

Betreuer*in: Leon Mayrhofer

Zeitraum: 01.11.2024 - 01.07.2025

MIDI ist ein Protokoll, mit dem Audiosignale digital übertragen werden können und das weit verbreitet ist. Ein mögliches Endgerät ist beispielsweise die Tesla-Spule aus dem Fachgebiet Hochspannungstechnische Betriebsmittel und Anlagen, mit der die empfangenen Töne abgespielt werden können.

Das Abspielen von bereits fertig codierten MIDI-Dateien stellt dabei keine große Herausforderung dar. Anders sieht es bei der Echtzeit-Verarbeitung und Ausgabe von live Aufnahmen aus. Als Beispiel-Instrument wurde für diese Arbeit ein Cello ausgewählt, dessen Musik auf der Tesla-Spule wiedergegeben werden soll. Zur Realisierung eines solchen Systems bietet sich ein FPGA mit einem SpartanMC Soft-Core für die allgemeine Kommunikation und einem dedizierten Hardwarebeschleuniger für die Konvertierung an.

Am Ende des Projektseminars sollte eine High-Level Software-Implementierung einer Verarbeitungs-Pipeline soweit auf einem normalen Rechner einsatzbereit sein, dass Cello-Aufnahmen über MIDI abgespielt werden können. Die Bearbeitung des Eingangssignals umfasst zuerst die Vorfilterung des Cello-Signals und anschließend die Konvertierung in die entsprechenden MIDI-Töne. Für eine feinere Auflösung der Töne in MIDI sollte das MIDI Pitch Bend feature implementiert werden.

Die anschließende Bachelor-Arbeit befasst sich mit der Portierung der High-Level Implementierung in ein auf einem Nexys Video-Board lauffähigen System. Dabei soll ein SpartanMC Prozessor die Kommunikation mit der Ausenwelt übernehmen und ein dedizierter Hardwarebeschleuniger befasst sich mit der Konvertierung des Cello-Signals zu MIDI.

Projektseminare Master

Student*in: Nora Simon

Betreuer*in: David Scheunert

Zeitraum: 30.10.2024 - 31.03.2025

Im Bereich der Entwicklung von Steuergeräten und eingebetteten Systemen hat sich seit einigen Jahren die Methodik "Hardware-in-the-loop" etabliert. Dabei wird ein Steuergerät nicht mit dem realen System verbunden, welches es kontrollieren soll, sondern mit einer Simulation dieses Systems. Diese Methodik lässt sich auch auf komplexe Regelungssysteme im wissenschaftlichen Bereich übertragen. So ist es denkbar, die Strahlregelung eines Cyclotrons nicht am realen Cyclotron auszutesten und zu entwickeln, sondern stattdessen ein Modell eines Strahls zu rechnen und somit die Strahlreaktion auf die Regelungseingriffe nur zu simulieren.

Aufgrund der großen Flexibilität des im Cavity-in-the-Loop-Projekt verwendeten Frameworks kann dieses auch für andere Aufgabenbereiche eingesetzt werden. Einer dieser Aufgabenbereiche ist die Echtzeitverarbeitung von Signalen bei der Messung von Schichtdicken durch Impulse im Terahertzbereich.

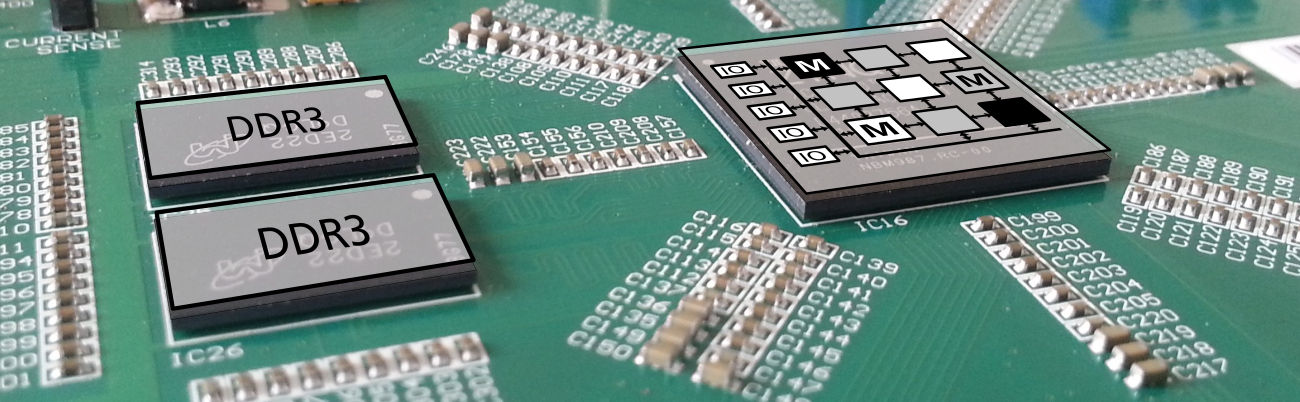

Damit das Framework auch für diesen Einsatzbereich verwendet werden kann, soll das ganze Projekt von einem AMD/Xilinx-VC707 auf einem AMD/Xilinx-VCU118 portiert werden. Dies ist notwendig, um genügend Ressourcen für die aufwendigere Berechnung zur Verfügung zu haben. Beim Portieren müssen hauptsächlich die Constraints sowie die Primitive angepasst werden. Außerdem muss ein Wechsel von DDR3 zu DDR4 realisiert werden

Weiterhin soll eine neue Analog-Digital-Wandler-FMC-Karte für das Projekt gesucht werden. Die bisher verwendete bietet eine deutlich zu hohe Sampling-Rate, dafür ist die Genauigkeit der einzelnen Messungen nicht genau genug.

In einer weiterführenden Masterarbeit kann weiter an dem Projekt der Terahertzmessungen gearbeitet werden.

Hiwi-Stellen

Student*in: Eric Schoch

Betreuer*in: M. Sc. Leon Mayrhofer

Zeitraum: 01.10.2024 - 31.03.2025

Am Fachgebiet werden WiiMote-Controller als Presenter für Vorlesungen verwendet. Die eingebaute Infrarot-Kamera wird dabei genutzt, um den Mauszeiger zu steuern. Das bisher genutzte Tool "wminput" wird leider nicht mehr weiterentwickelt und funktioniert unter aktuellen Ubuntu-Versionen nicht. Als aktuellere Alternative bietet sich das Tool "MoltenGamepad" an, welches jedoch nur eine eingeschränkte Maus-Unterstützung bietet.

Im Rahmen dieser Hiwi-Tätigkeit soll MoltenGamepad so erweitert werden, dass es den Input der Infrarot-Kamera auf die absolute Position des Mauszeigers abbildet. Dafür ist es notwendig, das Programm an mehreren Stellen zu erweitern. So ist z.B. die interne Rechnung von relativen auf absolute Koordinaten umzustellen und ein weiteres virtuelles Input-Device hinzuzufügen, welches absolute Maus-Koordinaten unterstützt.