Bachelor-Arbeiten

Student*in: Marius Ball

Betreuer*in: Ramon Wirsch

Zeitraum: 12.04.2021 - 11.10.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für verschiedene Prozessoren entwickelt. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardwarebeschleuniger zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können.

Um diverse Anwendungen und Benchmarks ausführen zu können, muss das Betriebsystem, mit dem diese Anwendungen kommunizieren, emuliert werden. Dies passiert idealerweise auf Ebene der Kernel-Calls, um unabhängig von etwaigen LibC-Implementierungen zu sein. Falls nicht möglich können aber auch LibC-Funktionsaufrufe abgefangen und emuliert werden, was bisher der Fall ist. Hierbei müssen aber meist ganze Klassen von Funktionen möglichst vollständigt abgefangen werden können, da sie sich meist internen Zustand teilen, der von der von abgefangen Aufrufen nicht gepflegt wird.

Da bereits zwei verschiedene Simulatoren (RISC-V, IBM-Z) entwickelt werden, sollte die Betriebsystem-Emulation so architektur-agnostisch wie möglich sein, um für beide Simulatoren gleichzeitig zu funktionieren.

Ziel dieser Arbeit ist es daher fehlende Funktionalität möglichst architektur-agnostisch in die Simulatoren nachzurüsten.

Student*in: Katharina Schultheis

Betreuer*in: Ramon Wirsch

Zeitraum: 21.06.2021 - 22.11.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Eine erste Fassung dieses Verfahrens läuft bereits, bei der der Assembler-Code in einen Kontrollflussgraphen (CFG) eingelesen wird und mithilfe einer Sammlung von Optimierungspasses für den Hardwarebeschleuniger optimiert wird. Hierbei muss der Hardwarebeschleuniger allerdings immer wieder auf den Stack des Host-Systems zugreifen, da der ursprüngliche Compiler hier zum Beispiel Funktionsargumente übergibt, oder Variablen, die nicht mehr in Register gepasst haben platziert hat.

Diese Stackzugriffe stellen einen Flaschenhals dar und sollen in dieser Arbeit so weit wie möglich durch Register-Zugriffe erstetzt werden.

Hierzu sollen Stack-Zugriffe analysiert werden, um notwendigerweise indirekte Zugriffe, wie auf Arrays, die auf dem Stack liegen, von Zugriffen auf skalare Werte zu unterscheiden. Anschließend sollen mindestens die skalaren Stack-Zugriffe durch Register-Zugriffe ersetzt werden. Manche Array-Zugriffe könnten eventuell in Kombination mit Loop-Unrolling ebenfalls eliminiert werden.

Student*in: Ann-Kathrin Werner

Betreuer*in: Dennis Wolf

Zeitraum: 01.11.2019 - 01.03.2021

Ein Coarse Grained Reconfigurable Array (CGRA) ist ein Hardwarebeschleuniger, in dem einzelne Rechenzellen entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel verarbeiten.

Eines unserer Forschungsthemen ist die Heterogenität von CGRAs. Um dies möglich zu machen, wurde ein Framework realisiert, mit dem beliebig heterogene und irreguläre CGRA modelliert werden können. Dieses Modell ist auch die Grundlage für das Scheduling und dient als Input um Verilog Code zu erzeugen. Da die jetzige Modellierung nicht flexibel genug ist und Änderungen an der Mikroarchitektur vorgenommen wurden, wird nun basierend auf der Erfahrung der letzten Jahre ein generisches, Ressourcen basiertes Modell umgesetzt. Der Kern des CGRAs und eine generische Schnittstelle wurden realisiert. Nun fehlen noch die Systemspezifischen Komponenten zur Integration des CGRAs in Amidar. Amidar ist ein am Lehrstuhl Rechnersystem entwickelter adaptiver Prozessor. Hierfür sollen Kommunikationsmodule automatisiert generiert werden, die die generischen Schnittstellen des CGRA Kerns bedient. Außerdem soll die Cache-Anbindung überarbeitet werden.

In dieser Arbeit soll die Systemintegration in Amidar durchgeführt werden und automatisierte Tests des CGRAs implementiert werden. Die Integration des alten CGRAs in Amidar kann hierfür als Vorlage genutzt werden. Zu Beginn soll manuell ein exemplarisches CGRA in Verilog umgesetzt und für eine simple Anwendung simuliert werden. Danach folgt die Integration in das Framework, so dass die Generierung der Kommunikationsschnittstellen für beliebige CGRAs automatisiert geschieht. Der Fokus der Arbeit soll abschließend ein Tool sein, das für gegebenen Java Applikationen, automatisierte Tests durchführt und die korrekte Funktionsweise des CGRAs inkl. der Kommunikationsschnittstellen prüft.

Student*in: Sebastian Kleemann

Betreuer*in: Alexander Schwarz

Zeitraum: 02.11.2020 - 01.04.2021

Derzeit wird am Fachgebiet Rechnersysteme an AMIDAR-Prozessoren geforscht, die aus mehreren unabhängigen Funktionseinheiten (FUs) aufgebaut sind und verschiedene Möglichkeiten der Rekonfiguration bereitstellen. Bisher lag der Fokus auf Ausführung von Java Bytecode, jedoch eignet sich das Grundprinzip für verschiedenste Instruktionssätze.

Nun wird die Idee verfolgt, eine speziell auf das AMIDAR-Konzept zugeschnittene Instruction Set Architecture (ISA) zu entwickeln, die einige Gedanken von Datenflussarchitekturen aufgreift. Für diesen Instruktionssatz wurde bereits ein funktionierender Prozessor auf einem FPGA implementiert.

Speziell für die FU, die den Java-Heap implementiert, bieten sich noch einige Verbesserungsmöglichkeiten, die im Rahmen dieser Arbeit umgesetzt werden sollen. Primär ist dies die Unterstützung echter Byte- und Short-Arrays, die derzeit noch durch Integer-Arrays realisiert sind.

Student*in: Maximilian Sexauer

Betreuer*in: Ramon Wirsch

Zeitraum: 19.04.2021 - 20.09.2021

Am Fachgebiet Rechnersysteme wird das SoC-Kit SpartanMC verwendet. Hierbei handelt es sich um ein speziell auf eingebettete Anwendungen auf FPGAs optimiertes System-On-Chip. Die Architektur des Prozessors weicht an einigen Stellen von herkömmlichen Prinzipien ab um die FPGA-Hardware optimal auszulasten. Aufgrund dieser Anpassungen funktionieren aber Features wie Debugging mit GDB nur beschränkt. Dies soll in dieser Arbeit verbessert werden.

Bei dem SpartanMC-Prozessor handelt es sich um eine 18-Bit Architektur. Da dies eine nicht übliche Breite ist, müssen die für SpartanMC relevanten 18-Bit in unterschiedlichen Formaten in vielfache von Bytes gepackt werden, meist 32-Bit. Dies sorgt allerdings für einen Unterschied in den Addressen, die vom Compiler und Debugger angenommen werden, im Vergleich zu den Addressen die auf dem Prozessor Anwendung finden. Da der Debugger aus dem laufenden System explizite Speicherbereiche ausliest, führen diese Unterschiede dazu, dass die falschen Addressen vom Debugger ausgelesen oder geschrieben werden.

Um dieses Problem zu beheben, muss an entsprechenden Stellen im Ablauf eine Address-Übersetzung stattfinden. Mögliche Stellen dafür sind im Compiler, der Debugging-Informationen in Form des DWARF2 Formats erzeugt, die die Addressen beschreiben sollen. Der Prozessor kann ebenfalls zur Laufzeit Addressen umrechnen und so dem Debugger ein unterstütztes, passendes Address-Layout vorspielen. Eine weitere Möglichkeit, die bisher noch nicht genutzt wird, ist ein Nachbearbeiten der DWARF2 Infos. Dies ist sinnvoll, weil der Compiler sehr komplex und nicht auf die Format-Änderungen ausgelegt ist. Der Prozessor hingegen hat als engebettetes Gerät nicht Zugriff auf alle nötigen Informationen, um alle Addressen korrekt umrechnen zu können.

Ziel dieser Arbeit ist es durch Nachbearbeiten der DWARF2 Debugging-Infos noch fehlende Debugging-Möglichkeiten umzusetzen. Hierbei soll insbesondere ermöglicht werden lokale Variablen, die sich allerdings auf dem Stack und nicht in Registern befinden, mit dem Debugger auslesen und bearbeiten zu können.

Student*in: Tobias Steinbach

Betreuer*in: Tobias Schladt

Zeitraum: 01.10.2021 - 27.12.2021

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund fehlender Erfahrungen mit der Integration von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Diese potentiellen Fehler müssen bei der Logiksynthese für NV-FPGAs beachtet werden.

Ziel dieser Arbeit ist es, fehlerbehaftete Look-Up-Tables (LUTs) in den Logiksynthese-Prozess des Tools "Versatile Place and Route" (VPR), das Teil der Toolchain "Verilog-to-Routing" (VTR) ist, zu integrieren.

Student*in: Niklas Mertens

Betreuer*in: Johanna Rohde

Zeitraum: 30.10.2020 - 29.01.2021

Ein Forschungsprojekt am Fachgebiet Rechnersysteme der TU Darmstadt befasst sich mit der automatischen Erzeugung von Hardwarebeschleunigern. Das entwickelte GCC-Plugin (PIRANHA) führt dazu eine statische Programmanalyse des Programmcodes durch und wählt eigenständig die Schleifen aus, die voraussichtlich die größte Ausführungszeit benötigen. Anschließend wird deren Funktionalität mit Hilfe einer High Level Synthese (HLS) als Hardwarebeschleuniger implementiert.

Der verfolgte Ansatz ist unabhängig vom Prozessor, an welchen die Beschleuniger angeschlossen werden. Gegenwärtig steht dafür unter anderem der MicroBlaze von Xilinx zur Verfügung.

Derzeit unterstützt PIRANHA nur Integer-Rechnung, obwohl der MicroBlaze an sich auch Floating Point Operationen verarbeiten kann. Dies hat zur Folge, dass potentielle Kernel, welche mit Floats arbeiten, nicht beschleunigt werden können.

Ziel dieser Bachelorarbeit ist es, den Floating Point Support in das PIRANHA HLS Plugin zu implementieren. Dafür ist die Operatorbibliothek sowohl Hardware- als auch Softwareseitig zu erweitern. Passende Implementierung von Floating Point Operationen stehen am FG Rechnersysteme zur Verfügung.

Master-Arbeiten

Student*in: Felix Hübner

Betreuer*in: Ramon Wirsch

Zeitraum: 19.10.2020 - 19.04.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt, unter anderem für die RISC-V Architektur. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie hierzu vorher angepasst werden müssen.

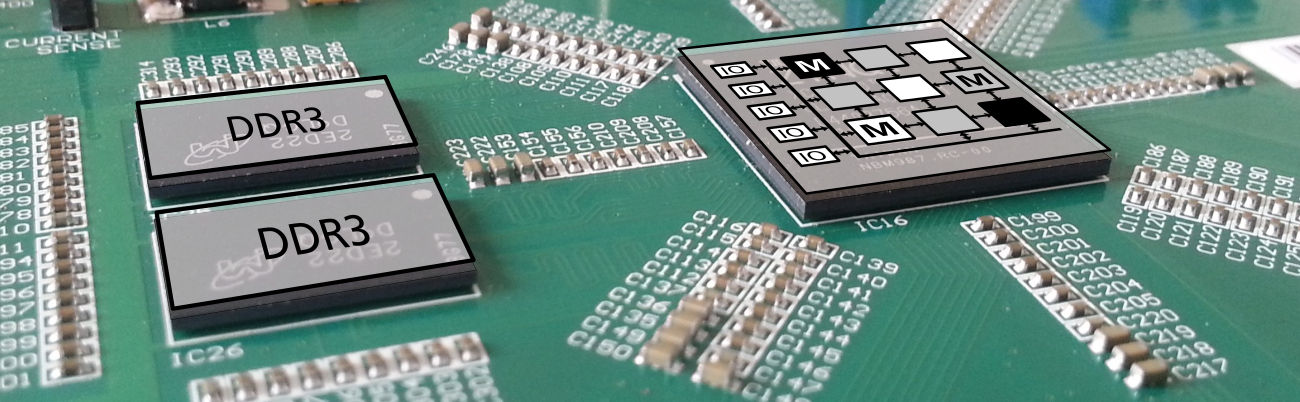

Um diese Verfahren zu testen und zu demonstrieren, soll ein vollständiges, lauffähiges System bestehend aus einem RISC-V Prozessor und unserem CGRA-Hardwarebeschleuniger auf einem FPGA gebaut werden. Dafür soll eine für FPGAs geeignete existierende RISC-V Implementierung ausgewählt werden.

Für ein lauffähiges System muss insbesondere der Beschleuniger cache-kohärenten Speicherzugriff auf den RAM erhalten, sowie als Peripherie an den Prozessor angebunden werden. Dies umfasst auch die Auswahl geeigneter Methoden zu Anbindung, sowie das Schreiben von Treibern, die Hardware spezifische Eigenheiten möglichst abstrahieren.

Student*in: Jonas Diegelmann

Betreuer*in: Ramon Wirsch

Zeitraum: 21.06.2021 - 20.12.2021

Am Fachgebiet Rechnersysteme werden eine Reihe von Architekturen mittels Coarse-Grained Reconfigurable Arrays (CGRAs) beschleunigt. Hierbei sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Das CGRA wurde ursprünglich für auf Java Bytecode basierende Architekturen entwickelt. Leider hat sich die aktuelle Umsetzung der Bedingungslogik (CBOX) für native Befehlssätze wie RISC-V als Flaschenhals herausgestellt. Limitierend sind hier unter anderem, wie viele Bedingungen effizient gleichzeitig ausgeliefert werden können. Außerdem können nur strikt geschachtelte Bedingungen auf der CBOX umgesetzt werden. Komplexere boolesche Logik muss im Kontrollflussgraphen (CFG) explizit umgeschrieben werden, um auf andere, breitere Einheiten (PEs) ausgelagert zu werden.

Der Scheduler enthält aktuell noch Sonderbehandlungen für die CBOX, die bei einem Neuentwurf vermieden werden könnten. Weiterhin werden bestimmte Features der Hardware zur Verkürzung von kritischen Pfaden vom aktuellen Scheduler noch nicht unterstützt.

Im Rahmen dieser Arbeit soll die Bedingungslogik des CGRAs neu entworfen werden. Sie soll dabei modularer und besser auf die Struktur von konventionellen Befehlssätzen und die Struktur der vorhanden CFGs angepasst werden.

Student*in: Johannes Klöhn

Betreuer*in: Ramon Wirsch

Zeitraum: 09.11.2020 - 17.05.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Eine erste Fassung dieses Verfahrens läuft bereits. Assemblercode wird dabei zur Laufzeit in einen Kontrollflussgraphen (CFG) eingelesen und mithilfe einer Sammlung von Optimierungspasses für den Hardwarebeschleuniger optimiert. Zurzeit werden allerdings noch alle Schreibzugriffe auf den Speicher in der originalen Reihenfolge ausgeführt und limitieren somit die möglichen Optimierungen. Dies ist nötig, da eine andere Reihenfolge potentiell zu falschen Ergebnissen kommen kann, wenn manche Speicherzugriffe überlappen.

Als Teil dieser Arbeit soll eine Points-To Analyse entwickelt werden, die auf Basis der existierenden CFGs versucht Überlappungen in Speicherzugriffen zu identifizieren. Diese Analyse soll möglichst unabhängig vom zugrunde liegenden Assembler-Befehlssatz sein, so dass sie auf den verschiedenen unterstützten Architekturen funktioniert und auch in der Lage sein, ähnliche Informationen zu verwenden, wie sie normalerweise vom Compiler bereitgestellt werden.

Die gewonnenen Informationen sollen anschließend genutzt werden, um die Reihenfolge von Speicherzugriffen zu lockern. Weiterhin kann in Fällen in denen Aliasing nicht ausgeschlossen werden kann, Spekulative Ausführung angewendet werden. Hier wird erst während der Ausführung eines Codeabschnittes auf Überlappung getestet und dann nur die dazu passende Variante des Abschnittes ausgeführt.

Student*in: David Volz

Betreuer*in: Johanna Rohde

Zeitraum: 06.11.2020 - 05.05.2021

Ein Forschungsprojekt am Fachgebiet Rechnersysteme der TU Darmstadt befasst sich mit der automatischen Erzeugung von Hardware-Beschleunigern. Das entwickelte GCC-Plugin führt dazu eine statische Programmanalyse des Programmcodes durch und wählt eigenständig die Schleifen aus, die voraussichtlich die größte Ausführungszeit benötigen. Anschließend wird deren Funktionalität mit Hilfe einer High Level Synthese (HLS) als Hardwarebeschleuniger implementiert.

Den Flaschenhals stellen dabei die Speicherzugriffe dar. Über ein Cache-System können zwar mehrere Speicherzugriffe gleichzeitig ausgeführt werden, dennoch kommt es bei Cache-Misses und dem anschließenden Laden aus dem Hauptspeicher zu langen Wartezeiten.

Die Anzahl an Cache-Misses kann durch Prefetching reduziert werden. Dabei werden zukünftige Speicheradressen antizipiert und während des Leerlaufs des Caches spekulativ geladen. Der Erfolg von Prefetching hängt maßgeblich davon ab, wie genau Speicheradressen vorhergesagt werden können. Ein Vorteil des High Level Synthese Tools besteht darin, dass die Speicherzugriffe der Hardware Beschleuniger bereits zur Compilezeit ausführlich analysiert werden. Die dabei gewonnenen Informationen könnten zum Prefetching verwendet werden.

Ziel dieser Arbeit ist es, eine Prefetch Engine für den Level-2 Cache des vorhandenen Cache-Systems zu implementieren und zu integrieren. Des Weiteren, sollen die generierten Hardware Beschleuniger gezielt um Prefetch-Instruktionen erweitert werden, welche an die Prefetch Egnine übergeben werden.

Voraussetzung für diese Masterarbeit ist der Level-2 Cache. Dieser kann im Vorfeld als Projektseminars implementiert werden.

Student*in: Jonas Gehrunger

Betreuer*in: Johanna Rohde

Zeitraum: 09.11.2020 - 10.05.2021

Ein Forschungsprojekt am Fachgebiet Rechnersysteme der TU Darmstadt befasst sich mit der automatischen Erzeugung von Hardware-Beschleunigern. Das entwickelte GCC-Plugin führt dazu eine statische Programmanalyse des Programmcodes durch und wählt eigenständig die Schleifen aus, die voraussichtlich die größte Ausführungszeit benötigen. Anschließend wird deren Funktionalität mit Hilfe einer High Level Synthese (HLS) als Hardwarebeschleuniger implementiert.

Eine Herausforderung besteht darin, die Abhängigkeiten von Lese- und Schreibzugriffen auf den Speicher zu bestimmen. Um die Semantik des Programms nicht zu verändern, müssen diese im konservativsten Fall im Beschleuniger in der gleichen Reihenfolge ausgeführt werden, wie in der Software beschrieben. Dies limitiert jedoch die Anzahl an parallel ausführbaren Instruktionen und stellt einen Flaschenhals dar.

Der GCC ermöglicht es, Speicherzugriffe umfassend zu charakterisieren. Diese Informationen werden derzeit dazu verwendet, möglichst viele Speicherzugriffe zur Compilezeit voneinander zu entkoppeln. Dies ist jedoch häufig nicht möglich, da es durch das Pointer-Aliasing dazu kommen kann, dass man über verschiedene Pointer auf den gleichen Speicher zugreift. Deswegen soll die Compilezeit-Analyse um eine Laufzeitanalyse erweitert werden. Dabei wird zur Compilezeit ein Satz an Bedingungen formuliert, deren Evaluation zur Laufzeit bestimmt, ob zwei Speicherzugriffe immer unabhängig voneinander sind. Bei einem positiven Ergebnis, kann dann ein optimierter Beschleuniger ausgeführt werden.

Aufgabe der Masterarbeit ist es, das Plugin so zu erweitern, dass möglichst viele Speicherzugriffe zur Laufzeit entkoppelt werden können. Dabei sollen insbesondere die Informationen zu Zugriffsmuster, Anzahl der Schleifeniterationen und Arraygröße herangezogen werden.

Die genauen Hintergründe zur Compilezeit-Analyse werden in diesem Paper beschrieben

Projektseminare Bachelor

Student*in: Nora Simon

Betreuer*in: Ramon Wirsch

Zeitraum: 12.02.2021 - 01.06.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt, unter anderem für die RISC-V Architektur. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Um den Gewinn der Laufzeitbeschleunigung praktisch testen und zeigen zu können, wird aktuell ein auf FPGAs lauffähiges System samt Beschleuniger entwickelt. Mit Taiga wurde bereits ein spezifischer RISC-V Prozessor ausgewählt, der zum aktuellen Zeitpunkt allerdings noch nicht über Fließkomma-Recheneinheiten verfügt. Diese sollen zu einem späteren Zeitpunkt nachgerüstet werden.

Um die Beschleunigung mit unserer Technik untersuchen und nachweisen zu können, ist es notwendig die Performance und das Verhalten des Beschleunigers und des Prozessors abzugleichen. Beispielsweise bringt es für die Beschleunigung nichts, wenn eine Komponente Rechenoperationen beherrscht, die das Gegenstück aber nicht unterstützt. Die dazu verwendeten Hardwareressourcen könnten anderweitig besser angelegt werden.

Im Rahmen dieser Arbeit sollen deshalb die existierenden Fließkomma-Operatoren des Beschleunigers, sowie andere zur Verfügung stehende oder von konkurrierenden Prozessoren verwendete Implementierungen untersucht und evaluiert werden. Besonders interessant ist hier beispielsweise die Unterstützung von denormalisierten Zahlen und Rounding-Modes, Operations-Latenzen, mögliches Pipelining, der Ressourcenverbrauch und maximaler Takt.

Student*in: Lukas Freiberger

Betreuer*in: Tobias Schladt

Zeitraum: 13.04.2021 - 13.07.2021

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, werden also bei Unterbrechung der Spannungsversorgung gelöscht. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund fehlender Erfahrungen mit der Integration von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Diese potentiellen Fehler müssen bei der Logiksynthese für NV-FPGAs beachtet werden.

In diesem Projektseminar sollen Alternativen zu den in FPGAs genutzten Look-Up-Tables im Hinblick auf ihre Fehlertoleranz untersucht werden. Dabei spielen alternative Funktionsdarstellungen, alternative Tabellenstrukturen sowie gänzlich neue Schaltungsstrukturen eine Rolle.

Student*in: Tobias Steinbach

Betreuer*in: Tobias Schladt

Zeitraum: 12.04.2021 - 12.07.2021

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, werden also bei Unterbrechung der Spannungsversorgung gelöscht. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund fehlender Erfahrungen mit der Integration von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Diese potentiellen Fehler müssen bei der Logiksynthese für NV-FPGAs beachtet werden.

In dieser Arbeit soll untersucht werden, inwiefern potentiell fehlerhafte Speicherzellen die Logik-Funktionen sowie das Placement und Routing für FPGAs beeinflussen. Dazu soll die Ausfallwahrscheinlichkeit einer Speicherzelle modelliert und in das FPGA-Modell einer bestehenden Logiksynthese-Toolchain (Verilog-to-Routing) integriert werden.

Projektseminare Master

Student*in: Simon Vetter

Betreuer*in: Ramon Wirsch

Zeitraum: 04.12.2020 - 01.03.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt, unter anderem für RISC-V und IBM Z-Architekturen. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Für die partielle Optimierung und Ausführung auf dem Beschleuniger müssen Code-Abschnitte zu einer speziellen Kontrollflussgraphendarstellung konvertiert werden. Hierzu müssen die Binärdaten in effizient maschinell verarbeitbare Instruktionen übersetzt werden. Anschließend können diese Instruktionen in die vorgegebene Darstellung in Static-Single-Assignment Form konvertiert werden, die alle nötigen Informationen enthält, um diesen Code zu testen, zu optimieren und auf den Beschleuniger abzubilden.

Im Rahmen dieser Arbeit soll der bestehende Konverter um die Dissassemblierung von üblichen x86 Programmen nachgerüstet werden. Damit würden 2 der popärsten CISC Architekturen unterstützt werden. Weiterhin soll die Implementierung mit den beiden existierenden Versionen für RISC-V und Z abgeglichen werden, um eine möglichst universelle Vorlage zur Umsetzung weiterer Architekturen zu erhalten.

Student*in: Felix Hübner

Betreuer*in: Ramon Wirsch

Zeitraum: 28.06.2021 - 01.11.2021

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt, unter anderem für die RISC-V Architektur. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie hierzu vorher angepasst werden müssen.

In einer anderen Arbeit wurde schon ein Demonstrationssystem bestehend aus dem Taiga RISC-V Prozessor und einem CGRA-Hardwarebeschleuniger erstellt. Noch ist dieses System allerdings nicht in der Lage den RISC-V Code zur Laufzeit mit alternativen Instruktionen zu überschreiben, die das CGRA als Hardwarebeschleuniger einsetzen.

Im Rahmen dieser Arbeit soll deshalb der Instruktions-Cache von Taiga zum Daten-Cache kohärent gemacht werden. Weiterhin muss auch auf die Kohärenz von weiteren Daten, wie denen des Branch-Predictors geachtet werden.

Die korrekte Funktionalität soll mit einem Beispiel-Programm nachgewiesen werden, das zuerst den original Code ausführt und anschließend den Code patched, um mit dem CGRA die 2. Ausführung zu beschleunigen.

Student*in: Erik Kubaczka

Betreuer*in: Tobias Schladt

Zeitraum: 01.12.2020 - 01.10.2021

Das Ziel der Synthetischen Biologie ist es, biochemische Systeme von Grund auf neu zu entwickeln. Dabei spielen neben biologischen und chemischen Verfahren Methoden aus den Ingenieurswissenschaften und der Informationstechnik eine entscheidende Rolle. So wird unter anderem daran geforscht, digitale Schaltungen auf Basis genetischer Mechanismen in biologischen Zellen zu implementieren.

Für die Synthese dieser genetischen Schaltkreise kommen bisher vor allem Verfahren zum Einsatz, die nicht an die Rahmenbedingungen der Synthetischen Biologie angepasst sind. So ist die Bibliothek zur Verfügung stehender Logikgatter stark eingeschränkt und es kommt zu komplexen biochemischen Wechselwirkungen zwischen einzelnen Bausteinen. Die Robustheit einzelner Schaltungsimplementierungen kann dabei durch Simulation ermittelt werden. Das Technology Mapping, also die Wahl von Bibliotheksgattern als Realisierungen für Gatter der Schaltung, stellt somit ein kombinatorisches Optimierungsproblem dar.

In dieser Arbeit soll ein Technology Mapping-Algorithmus für genetische Schaltkreise auf Basis des Branch-and-Bound-Ansatzes entwickelt werden. Dieser soll Teillösungen mit Hilfe eines optimistischen Schätzers bewerten und gegebenenfalls vom weiteren Suchprozess ausschließen.