Bachelor Theses

Student: Nikolai Shauchenka

Supervisor: Leon Mayrhofer

Time period: 09/01/2025 - 03/02/2026

MIDI ist ein Protokoll, mit dem Audiosignale digital übertragen werden können und das weit verbreitet ist. Ein mögliches Endgerät ist beispielsweise die Tesla-Spule aus dem Fachgebiet Hochspannungstechnische Betriebsmittel und Anlagen, mit der die empfangenen Töne abgespielt werden können.

Das Abspielen von bereits fertig codierten MIDI-Dateien stellt dabei keine große Herausforderung dar. Anders sieht es bei der Echtzeit-Verarbeitung und Ausgabe von live Aufnahmen aus. Als Beispiel-Instrument wurde für diese Arbeit ein Cello ausgewählt, dessen Musik auf der Tesla-Spule wiedergegeben werden soll. Zur Realisierung eines solchen Systems bietet sich ein FPGA mit einem SpartanMC Soft-Core für die allgemeine Kommunikation und einem dedizierten Hardwarebeschleuniger für die Konvertierung an.

Im Rahmen eines vorgeschalteten Projektseminars ist eine High-Level Software-Implementierung einer Verarbeitungspipeline erstellt worden, die auf einem normalen Rechner läuft und Cello-Aufnahmen über MIDI abgespielen kann. Die Bearbeitung des Eingangssignals umfasst zuerst die Vorfilterung des Cello-Signals und anschließend die Konvertierung in die entsprechenden MIDI-Töne. Für eine feinere Auflösung der Töne in MIDI sollte das MIDI Pitch Bend feature implementiert werden.

Aufbauend auf den Ergebnissen des vorangegangenen Projektseminars soll im Rahmen dieser Bachelor-Arbeit das bestehende High-Level System in ein auf einem Nexys Video-Board lauffähiges System portiert werden. Dabei soll ein SpartanMC Prozessor die Kommunikation mit der Ausenwelt übernehmen und ein dedizierter Hardwarebeschleuniger befasst sich mit der Filterung des Cello-Signals und der Konvertierung zu MIDI.

Student: Michael Peter

Supervisor: Katharina Schultheis

Time period: 12/11/2025 - 05/13/2026

In FPGAs werden zur Speicherung der Konfigurationsdaten typischerweise SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind elektronische Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen defektbehaftet ist. Diese potentiellen Defekte müssen im Entwurf von NV-FPGAs berücksichtigt werden. Daher wird derzeit an alternativen Architekturen sowohl für Logikblöcke als auch Routing-Netzwerke geforscht. Im Zuge dessen müssen auch die Tools für die Logiksynthese angepasst oder neu entwickelt werden.

Im Rahmen dieser Arbeit soll ein bereits existierendes Technology Mapping-Verfahren um ein Verbindungsnetzwerk erweitert werden, welches es ermöglicht, innerhalb dieses Netzwerkes Signale kombinatorisch zu verknüpfen. Hierfür muss das Mapping von Funktionen angepasst werden, sodass von diesen Verbindungen Gebrauch gemacht werden kann.

Student: Patrick Pretschner

Supervisor: Jonas Gehrunger

Time period: 02/09/2026 - 08/10/2026

Am Fachgebiet Rechnersysteme wird im Rahmen des (EES)²-Projektes die Hardware-Beschleunigung der Schaltungssimulation von Memristoren mithilfe der Software SPICE [1] untersucht. Dabei sollen neben dem aus der Schaltung abgeleiteten Gleichungssystem Modelle der Schaltungselemente in einem Hardwarebeschleuniger parallelisiert ausgewertet werden.

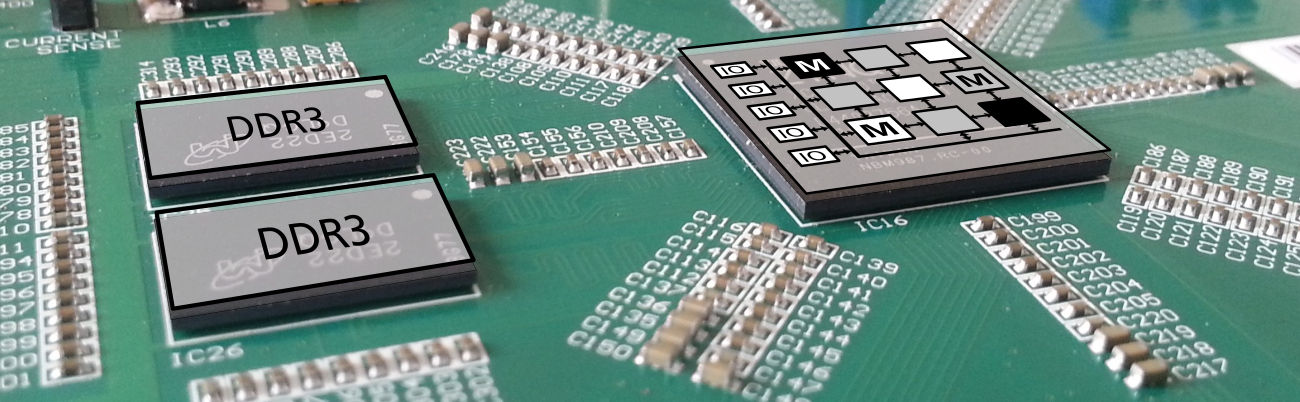

Für das Lösen des linearen Gleichungssystems innerhalb einer Simulations-Iteration sowie für die Linearisierung der Modelle wurden in vorangehenden Arbeiten bereits ein Beschleuniger implementiert und die Anbindung an den Host-PC umgesetzt. Für die bessere Verwendbarkeit der Hardware soll nun ein gemeinsames Speichersystem zur Verbindung der einzelnen Komponenten aufgebaut werden. Dafür müssen sowohl für jeden Zeitschritt die zur Linearisierung notwendigen Daten zu den einzelnen Modell-Recheneinheiten als auch die Rechenergebnisse zurück an Speicher und Host-PC-Interface transportiert werden. Zusätzlich ist es notwendig, mit der begrenzten Anbindung an den außerhalb des FPGAs befindlichen DDR4-DRAMs optimal umzugehen und Zwischenspeicher, Prefetching und Priorisierung der Zugriffe einzusetzen. Innerhalb des FPGAs existieren verschiedene Speicherarten (u.a. BRAM und URAM), die sich hierbei anbieten.

In dieser Arbeit soll der Austausch von Daten zwischen verschiedenen Teilen der in der Hardware-Beschreibungssprache Chisel auf dem FPGA implementierten SPICE Simulation, dem Off-Chip Memory und dem Host-Beschleuniger-Interfaces realisiert werden.

Master Theses

Student: Rocío Dominguez Moa

Supervisor: Katharina Schultheis

Time period: 11/26/2025 - 05/26/2026

In traditional Field Programmable Gate Arrays (FPGAs), Look-Up-Tables (LUTs) are used to realize logic functions. They contain SRAM-based memory cells which store a design's configuration data. This memory type is volatile, i.e. data is lost as soon as the device’s power supply is disrupted and consequently needs to be rewritten during each power up. As an alternative, Non-Volatile (NV)-FPGAs are a current research topic. One technology that allows the realization of non-volatile memory cells is the use of memristors.

The memristor is an electrical component whose resistance depends on the history of current flowing through it. Due to its fabrication process, a number of memristors will likely be defective. Even a single damaged memory cell reduces the usability of a traditional LUT significantly. Therefore, an alternative architecture for FPGA logic elements is being developed which is more resilient to those defects. Since state-of-the-art FPGA synthesis tools only support technology mapping to LUTs, new approaches need to be developed which are suited for those alternative architectures.

The goal of this thesis is the development and evaluation of such a technology mapping approach.

Project Seminars Bachelor

Student: Zoe Reigl

Supervisor: Jonas Gehrunger

Time period: 11/14/2023 - 04/02/2026

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Für den SpartanMC werden die Toolchains verschiedener FPGA-Hersteller, unter anderem von Xilinx/AMD und Altera/Intel, unterstützt. Der chinesische Hersteller Gowin stellt kompakte und günstige FPGAs her, die gut für die Anwendung in eingebetteten Anwendungen geeignet sind. Die verfügbaren Primitive in Gowin-FPGAs unterscheiden sich jedoch von denen, die etwa in Xilinx-FPGAs anzutreffen sind.

Ziel dieses Projektseminars ist es, das SoC-Kit und den SpartanMC Soft-Core auf FPGAs der LittleBee-Familie des Herstellers Gowin zu portieren. Dazu soll zunächst der SpartanMC Soft-Core zur Nutzung der Gowin-Primitive angepasst und anschließend die Unterstützung für die Gowin-EDA Toolchain in das SoC-Kit integriert werden.

Aufbauend auf diesem Projektseminar soll innerhalb einer Bachelorarbeit die korrekte Funktion der Portierung durch den Aufbau eines Demonstrators nachgewiesen werden. Details dazu finden sich hier. Das Projektseminar wird nur in Zusammenhang mit der Bachelorarbeit vergeben.

Student: Eric William

Supervisor: Jonas Gehrunger

Time period: 08/29/2025 - 02/27/2026

Am Fachgebiet Rechnersysteme wird im Rahmen des (EES)²-Projektes die Hardware-Beschleunigung der Schaltungssimulation von Memristoren mithilfe der Software SPICE [1] untersucht. Dabei sollen neben dem aus der Schaltung abgeleiteten Gleichungssystem Modelle der Schaltungselemente in einem Hardwarebeschleuniger parallelisiert ausgewertet werden. Um mit dem Nutzer zu interagieren und Simulationsdaten vorzubereiten wird die Open-Source SPICE Implementation ngspice verwendet.

Zur Verifikation des Beschleunigers ist es notwendig, das Zusammenspiel mit der Software auf dem Host-PC zu überprüfen. Hierzu ist es aktuell notwendig, bei jeder Änderung eine Synthese für das physikalische FPGA abzuwarten. Um Zeit zu sparen und Änderungen schneller testen zu können, soll in dieser Arbeit ein Interface entwickelt werden, dass eine Co-Simulation von Software und Hardwarebeschleuniger ermöglicht. Dazu muss für den Simulator QuestaSim ein Interface ergänzt werden, dass Daten von einer C/C++-Bibliothek entgegennimmt und innerhalb der Simulation in den Speicher schreibt und die Simulation automatisch unterbricht, wenn kein Beschleuniger gebraucht wird.

Student: Lea Horn

Supervisor: David Scheunert

Time period: 06/03/2025 - 04/06/2026

Project Seminars Master

Student: Laurenz Lemke

Supervisor: David Scheunert

Time period: 04/01/2026 - 10/01/2026

Student: Cagri Ipek

Supervisor: Jonas Gehrunger

Time period: 04/15/2024 - 08/15/2024

In FPGAs werden zur Speicherung der Konfigurationsdaten typischerweise SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen aus Memristoren dar.

Memristoren sind elektrische Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen defektbehaftet ist. Diese potentiellen Defekte müssen im Entwurf der Architektur und Synthese-Werkzeuge für NV-FPGAs berücksichtigt werden.

In vorhergehenden Arbeiten wurde gezeigt, dass traditionelle Routing-Elemente, die auf mehrstufigen Multiplexern basieren, besonders intolerant gegenüber defekten Speicherzellen sind. Daraufhin wurde eine neue Architektur für diese Switchbox-Elemente entwickelt, die Memristoren im Signalpfad verwendet. In Simulationen auf Architekturebene hat sich gezeigt, dass dies die Defekttoleranz deutlich steigert.

In diesem Projektseminar sollen zunächst die verfügbaren Modelle zur Schaltungssimulation von Memristoren untersucht werden. Für verschiedene Materialien und Verfahren soll dabei jeweils die Stabilität, Genauigkeit und Geschwindigkeit der verfügbaren Schaltungsmodelle evaluiert und analysiert werden. Aufbauend auf den Ergebnissen soll im Rahmen einer Masterarbeit dann die analoge Simulation von Switchbox-Elementen in FPGAs für verschiedene Bauteilparameter von Memristoren durchgeführt werden.

Student: Paul Rogalla von Bieberstein

Supervisor: Leon Mayrhofer

Time period: 11/01/2025 - 04/01/2026

Am Fachgebiet Rechnersysteme wird ein eigener RISC-V Soft-Core in Chisel entwickelt. Dieser dient vorwiegend für die Verwendung in FPGAs. Aufgrund dieser Zielausrichtung bietet es sich an, einen Soft-Core-Generator zu implementieren, mit dem der RISC-V Prozessor an die anwendungsspezifischen Anforderungen angepasst werden kann.

Bisher ist der RISC-V Soft-Core in einer sehr einfachen Basisvariante implementiert. Nicht alle in der RISC-V Basisspezifikation definierten Integer-Operationen sind umgesetzt. Des weiteren sind bisher keine erweiterten Funktionen wie beispielsweise eine Floating-Point-Recheneinheit vorhanden. Die Aufgabe in diesem Master-Projektseminar besteht in einer Analyse der vorhandenen Implementierung bezüglich fehlender Integer-Operationen, dem geschätzten Aufwand, diese zu inkludieren, und der Erstellung eines Plans zur Realisierung der standardisierten Floatingpoint-Extension mit der Erweiterung, dass arbiträre Bitbreiten verwendet werden können.

Der Aspekt des Generierens von verschiedenen Ausbaustufen des RISC-V Soft-Cores kann durchaus elegant durch den Einsatz der Chisel HDL erreicht werden. Chisel arbeitet auf einer höheren Abstraktionsebene als zum Beispiel Verilog oder VHDL und erlaubt es mit sehr wenig Aufwand einfach zu konfigurierende generische Module zu erstellen. Da das bereits vorhandene System in Chisel vorliegt, ist der Einsatz von Chisel bei dieser Arbeit verpflichtend. Es werden allerdings auch Verilog-Kenntnisse vorausgesetzt, da Chisel-Code vor der Synthese zu Verilog konvertiert wird.

Student: Mehmet Can Kivanc

Supervisor: Jonas Gehrunger

Time period: 12/16/2024 - 03/30/2026

Am Fachgebiet Rechnersysteme wird im Rahmen des (EES)²-Projektes die Hardware-Beschleunigung der Schaltungssimulation von Memristoren mithilfe der Software SPICE [1] untersucht. Dabei sollen neben dem aus der Schaltung abgeleiteten Gleichungssystem Modelle der Schaltungselemente in einem Hardwarebeschleuniger parallelisiert ausgewertet werden.

Bei der Simulation wird für jeden Zeitschritt ein lineares Gleichungssystem aufgestellt, das gelöst werden muss. In einer vorhergehenden Arbeit wurde der KLU-Solver, ein Lösungsverfahren für dünnbesetzte lineare Gleichungssysteme, implementiert. Ebenfalls liegt bereits ein grundlegendes Host-Beschleuniger Interface via Ethernet vor.

In dieser Arbeit soll die in KLU vorgesehene symbolische Analyse der Gleichungssystemstruktur in die Host-Software integriert und anschließend die notwendigen Daten zur Lösung des im Beschleuniger erzeugten Gleichungssystems über das PC-Interface übertragen werden. Abschließend muss der KLU-Solver selbst in den Simulations-Ablauf im SPICE-Hardwarebeschleuniger eingebunden und die Steuerung ergänzt werden.