Bachelor Theses

Student: Eric Schoch

Supervisor: Ramon Wirsch

Time period: 04/24/2023 - 07/24/2023

Am Fachgebiet Rechnersysteme werden Hardware-Beschleuniger für verschiedene Prozessorarchitekturen entwickelt. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardware-Beschleuniger zur Laufzeit analysiert und partiell mit diesem ausgeführt werden können.

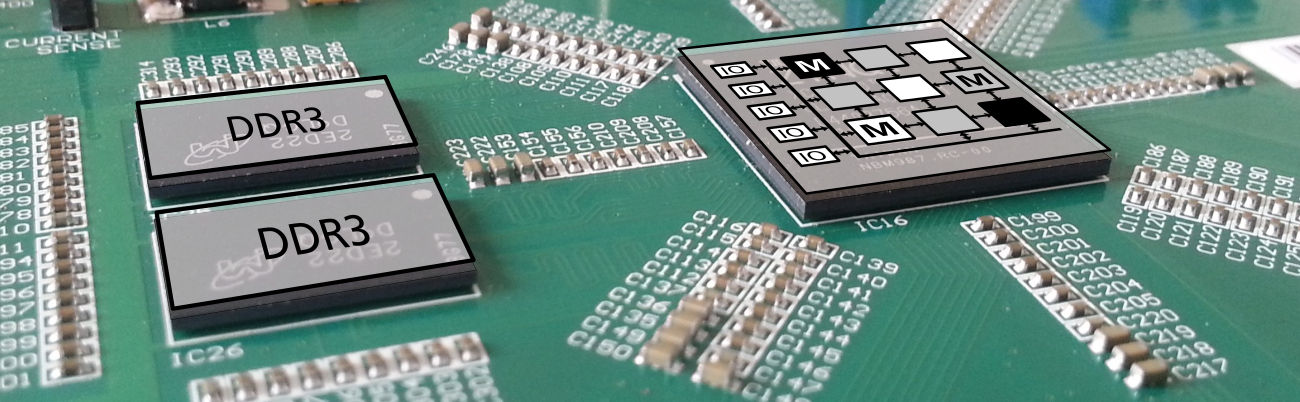

Eines der Teilsysteme für diese Hardware-Beschleunigung ist das RV-CGRA SoC, dass unter anderem einen Taiga/CVA5 RISC-V Prozessor enthält. Dabei handelt es sich um ein Embedded-System das bisher hauptsächlich ohne Betriebsystem oder mit dem Echtzeitbetriebssystem Zephyr betrieben wurde. Viele für die Hardwarebeschleunigung interessante Benchmarks benötigen Zugriff auf Dateien, so dass sie zum Beispiel eine Video-Datei wie auf einem Linux-System öffnen können. Diese sind deshalb bisher nicht ohne aufwendige Code-Änderungen für jeden Benchmark ausführbar.

Ziel dieser Arbeit ist die Erweiterung des existierenden Systems um eine Möglichkeit, Dateien identisch oder sehr ähnlich zur libc aus C-Code verarbeiten zu können. Eine vorherige Arbeit hat gezeigt, dass die Anbindung der existierende Systeme via LAN-Anschluss an einen Host-PC samt einer Software auf dem Host-PC am vielversprechendsten ist. Die genaue Verteilung der Aufgaben zwischen Host-PC und Embedded-System kann selbst gewählt werden.

Student: Lukas Pajak

Supervisor: Ramon Wirsch

Time period: 04/14/2023 - 07/24/2023

Am Fachgebiet Rechnersysteme werden Hardware-Beschleuniger für verschiedene Prozessorarchitekturen entwickelt. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardware-Beschleuniger zur Laufzeit analysiert und partiell mit diesem ausgeführt werden können.

Eine Form dieser Beschleuniger ist das CGRA, das sich insbesondere durch seine Parallelität mit vielen gleichzeitig arbeitenden Recheneinheiten auszeichnet. Die Recheneinheiten arbeiten aber nicht unabhängig voneinander, sondern müssen regelmäßig, taktgenau Daten zwischeneinander austauschen. Das Debuggen von Programmen, sogenannten Kerneln, für diese Hardwarebeschleuniger ist dementsprechend schwer.

Im Rahmen dieser Arbeit soll ein grafisches Tool entwickelt werden, um die Kernel für das CGRA nachzuvollziehen. Es soll möglich sein, jeden einzelnen Zeitschritt des Kernels detailliert, grafisch darzustellen und die exakten Tätigkeiten jeder einzelnen Einheit zu erkennen und sich schrittweise durch die Zeitschritte zu bewegen.

Die CGRA-Programme werden automatisch von einem Scheduler erzeugt. Deshalb soll die grafische Darstellung auch Informationen des Schedulers über die Erstellung des Programms nutzen können. So können Nutzer besser nachvollziehen, warum zum Beispiel eine bestimmte Operation nur auf einer bestimmten Einheit ausgeführt werden kann oder warum der Beschleuniger auf spezifische Daten warten muss. Auf der Suche nach Fehlern können so schneller unerwartete Scheduling-Entscheidungen identifiziert werden.

Es existiert bereits ein taktgenauer Simulator des CGRAs, der genutzt werden kann, um auch echte Werte aus der Simulation in die Darstellung zu integrieren. So könnte das Tool bis hin zu einem vollständigem Debugger für den CGRA ausgebaut werden.

Student: Mohamed Saleh

Supervisor: Tobias Schwarz

Time period: 04/18/2023 - 09/19/2023

Am Fachgebiet Rechnersysteme wird ein Verfahren zur Abbildung digitaler Entwürfe auf FPGA-Technologie entwickelt, das Binary Decision Diagrams (BDDs) als Zwischendarstellung nutzt. Ein entscheidender Faktor für die Laufzeit des Verfahrens ist die Performanz der BDD-Erzeugung. Aktuell wird eine in Kotlin geschriebene Bibliothek verwendet, die aus in BLIF beschriebenen Entwürfen BDDs generiert. Diese weist für Funktionen mit vielen Variablen eine sehr große Laufzeit auf, was die Abbildung von komplexen Entwürfen erschwert oder verhindert.

Das Ziel dieser Bachelorarbeit ist die Optimierung der BDD-Bibliothek, sodass diese auch aus komplexen Entwürfen BDDs generieren kann. Für die Bearbeitung sind Vorkenntnisse in Kotlin sowie sehr gute Programmierkenntnisse gute Voraussetzungen.

Student: Mehmet Can Kivanc

Supervisor: Jonas Gehrunger

Time period: 04/24/2023 - 09/25/2023

Es gibt zahlreiche Formate, um Zahlen mit Nachkommastellen darzustellen. Am häufigsten sind dabei Fließkommazahlen nach der IEEE 754 Norm anzutreffen. Diese Darstellung hat allerdings mehrere Nachteile, die die alternative Darstellung Posit interessant machen. Posits können etwa bei gleicher Breite einen größeren Wertebereich und eine bessere Präzision abbilden. Vorhandene Hardware-Implementationen wie z.B. PACoGen benötigen bisher im Vergleich allerdings fast die doppelte Fläche.

Daher soll in dieser Arbeit die vorhandene Hardware-Implementation PACoGen angepasst werden, um nur diskrete Regime-Breiten zu unterstützen. Dies reduziert die Komplexität der erzeugten Hardware und damit die benötigte Fläche, schränkt aber auch den Wertebereich ein. Dieser Trade-Off soll genauer untersucht werden.

Master Theses

Student: Daniel Stein

Supervisor: Ramon Wirsch

Time period: 10/13/2022 - 04/12/2023

Am Fachgebiet Rechnersysteme werden Hardware-Beschleuniger unter anderem für einen RISC-V Prozessor entwickelt. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardware-Beschleuniger zur Laufzeit analysiert und partiell mit diesem ausgeführt werden können.

Es existiert bereits ein FPGA-basiertes SoC inklusive des Beschleunigers. Bei der Entwicklung hat sich aber ein Flaschenhals an den Speicherschnittstellen des Beschleunigers herausgestellt. Um Fehlerfreiheit bei Cache-/Speicherzugriffen zu garantieren, dürfen Zugriffe zur Zeit nicht parallel ausgeführt werden.

Im Rahmen dieser Arbeit soll sowohl der Scheduler, als auch die Hardware um Möglichkeiten für eine neue Synchronisierung ergänzt werden. Der Scheduler soll Speicheroperationen gesondert betrachten und Wege bereitstellen, wie ihm potentielle Konflikte, Überlappungen oder auch garantierte Konfliktfreiheit zwischen Speicherzugriffen mitgeteilt werden können. Der Scheduler muss dann die Zugriffe so auf die verschiedenen Speicherzugriffseinheiten und Caches verteilen, dass Konflikte ausgeschlossen werden können. Für den Fall, dass es nicht möglich ist Konflikte statisch auszuschließen, soll der Scheduler granulare "Speicherbarrieren" einsetzen, die warten, bis die potentiell in Konflikt stehenden Transaktionen vollständig abgeschlossen wurden.

Für die Umsetzung dieser Barrieren muss die Hardware erweitert werden. Eine bedingte Umsetzung, bei der zur Laufzeit auf Konflikte getestet wird, um die Anzahl an Stalls zur Vermeidung von Konflikten zu reduzieren, könnte gerwinnbringend sein.

Weiterhin sollen bei diesen Änderungen auch verwandte Probleme gelöst werden. Cache-Prefetch Operationen brauchen nur geschedulet werden, wenn sie in den Schedule passen ohne diesen signifikant zu verlängern. Die Adressberechnung, bestehend aus Basisadresse und Offset findet aktuell als Teil des Speicherzugriffes statt und liegt auf dem kritischen Pfad. Gerade weil die finale Addresse aber eventuell für Überlackungschecks zur Laufzeit benötigt werden, macht es unter Umständen Sinn, diese Berechnung als getrennte Operation auszulagern, dies hängt aber von der Umsetzung der bedingten Speicherbarrieren ab.

Student: Sebastian Kleemann

Supervisor: Ramon Wirsch

Time period: 11/21/2022 - 05/22/2023

Am Fachgebiet Rechnersysteme werden Coarse Grained Reconfigurable Array Beschleuniger unter anderem für einen RISC-V Prozessor entwickelt. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardware-Beschleuniger zur Laufzeit analysiert und partiell mit diesem ausgeführt werden können.

Der Prozessor verfügt bereits über eine Fließkommaimplementierung auf Basis von optimierten FloPoCo-Operatoren. Das CGRA beherrscht auch bereits Fließkommazahlen, allerdings mit einer im Fließkommaformat konfigurierbaren, aber für aktuelle Zwecke ineffizienten Fließkommaimplementierung. Für eine bessere Vergleichbarkeit zwischen CGRA und Prozessor, um so besser eine Beschleunigung mittels CGRA aufgrund von Parallelisierung nachzuweisen, soll der CGRA an den Prozessor angeglichen werden.

Hierzu muss das FloPoCo-Framework um noch fehlende Funktionalität erweitert werden. Alle Single-Precision Fließkommaoperationen auf dem CGRA sollen dann durch FloPoCo-Varianten ersetzt werden. Für eine optimale Nutzung mit FloPoCo sollen die Registerfiles des CGRAs, wie beim Prozessor verbreitert werden. Zusammen mit der Inbetriebnahme von gepipelinten Registerfiles sollten sich so die meisten Flaschenhälse des CGRAs gelöst werden und das CGRA deutlich höhere Frequenzen erreichen.

Student: Christoph Flothow

Supervisor: Tobias Schwarz

Time period: 05/10/2023 - 11/08/2023

Am Fachgebiet Rechnersysteme wird zur Logiksynthese für Field Programmable Gate Arrays (FPGAs) geforscht. Einen Schwerpunkt bildet dabei das Technology Mapping, bei dem eine Boolesche Beschreibung der gewünschten Funktionalität auf Elemente der Zieltechnologie abgebildet wird. Den Kern des Technology Mappings für FPGAs bildet die Abbildung auf Lookup-Tables (LUTs). Im Rahmen eines Projektseminars am Fachgebiet wurde ein Mapper für LUTs entwickelt, der als Zwischendarstellung Binary Decision Diagrams (BDDs) verwendet. Mit Hilfe von Modifikationen der BDDs werden in diesem Verfahren die Eingabefunktionen dekomponiert und eine Zuordnung der Booleschen Variablen auf LUTs vorgenommen.

Im Rahmen dieser Arbeit soll das vorhandene Verfahren dahingehend erweitert werden, dass es mit beliebig strukturierten Eingabefunktionen funktioniert. Dazu sollen bekannte Probleme des Verfahrens analysiert und gelöst werden, sowie neue Strategien implementiert werden, um eine gesteigerte Lösungsqualität zu erreichen.

Student: David Scheunert

Supervisor: Jonas Gehrunger

Time period: 05/02/2023 - 10/30/2023

Im Bereich der Entwicklung von Steuergeräten und eingebetteten Systemen hat sich seit einigen Jahren die Methodik "Hardware-in-the-loop" etabliert. Dabei wird ein Steuergerät nicht mit dem realen System verbunden, welches es kontrollieren soll, sondern mit einer Simulation dieses Systems. Diese Methodik lässt sich auch auf komplexe Regelungssysteme im wissenschaftlichen Bereich übertragen. So ist es denkbar, die Strahlregelung eines Cyclotrons nicht am realen Cyclotron auszutesten und zu entwickeln, sondern stattdessen ein Modell eines Strahls zu rechnen und somit die Strahlreaktion auf die Regelungseingriffe nur zu simulieren.

Am Fachgebiet Rechnersysteme wird seit mehreren Jahren an Coarse Grained Reconfigurable Arrays (CGRA) als Rechenbeschleuniger geforscht. Dabei wurde in einem vorhergehenden Projekt auch schon ein physikalisches Modell in einem industriellen Umfeld in Echtzeit simuliert. CGRAs haben also bereits bewiesen, dass sie für den Einsatz in Echtzeitsystemen gut geeignet sind. Es bietet sich daher an, die Strahlsimulation ebenfalls mithilfe von CGRAs zu realisieren.

Im Rahmen dieser Arbeit soll ein CGRA basierter Strahlsimulator entworfen, anhand mehrerer Anwendungsfälle verifiziert und in der GSI an einem realen Strahlregelungssystem getestet werden.