Bachelor Theses

Student: Nico Eberlein

Supervisor: Boris Dreyer

Time period: 02/01/2015 - 04/30/2015

Für die Korrektheit von sicherheitskritischen eingebetteten Systemen ist es nicht nur wichtig, dass Programme korrekte Ergebnisse berechnen, sondern dass sie diese auch rechtzeitig liefern. Um dies sicherzustellen, muss die Worst Case Execution Time (WCET) des Programms bestimmt werden. Die WCET eines Programms setzt sich aus der WCET von einzelnen Basic Blocks (BB) zusammen. Ein BB ist eine nicht verzweigende Sequenz von Instruktionen. Ein Programm besteht daher aus hunderttausenden von BBs.

Mittels dynamischer Programmanalyse kann die WCET und weitere Zeiten eines Programms gemessen werden. Hierbei wird die Ausführungszeit eines jeden einzelnen BBs gemessen und eine Statistik geführt. Diese Statistik enthält für jeden BB die WCET, die Average Case Execution Time (ACET) und die Best Case Execution Time (BCET). Anschließend können durch entsprechende Kombination der BB-Statistiken anhand des Programmablaufplans Rückschlüsse auf die Ausführungszeit des Programms gezogen werden.

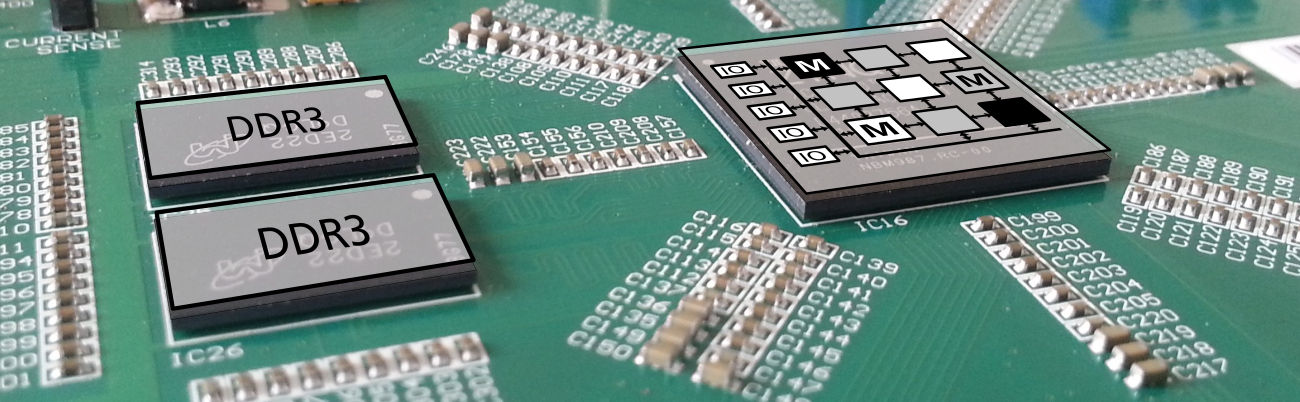

Da ein Programm aus hunderttausenden von BBs besteht, kann die Statistik aufgrund ihrer Größe nicht im BRAM oder distributed RAM eines FPGAs gehalten werden, sondern muss in externen RAM ausgelagert werden.

Das Ziel dieser Arbeit ist das Design und die Implementierung eines Hardware-Statistik-Moduls für die dynamische Programmanalyse. Neben einer Schnittstelle, über die das Modul die erhobene Statisik nach einer Programmanalyse einem weiteren Modul zur Verfügung stellt, muss das Hardware-Statistik-Modul eine Schnittstelle bereitstellen, über das es während der dynamischen Programmanalyse, die IDs der BBs und deren jeweils gemessen Ausführungszeiten entgegennehmen kann.

Student: Stefan Knipp

Supervisor: Boris Dreyer

Time period: 02/01/2015 - 06/30/2015

Für die Korrektheit von sicherheitskritischen eingebetteten Systemen ist es nicht nur wichtig, dass Programme korrekte Ergebnisse berechnen, sondern, dass sie diese auch rechtzeitig liefern. Um dies sicherzustellen, muss die Worst Case Execution Time (WCET) des Programms bestimmt werden. Die WCET eines Programms setzt sich aus der WCET von einzelnen Basic Blocks (BB) zusammen. Ein BB ist eine nicht verzweigende Sequenz von Instruktionen. Ein Programm besteht daher aus hunderttausenden von BBs.

Mittels dynamischer Programmanalyse kann die WCET und weitere Zeiten eines Programms gemessen werden. Hierbei wird die Ausführungszeit eines jeden BBs gemessen und eine Statistik geführt. Diese Statistik enthält für jeden BB die WCET, die Average Case Execution Time (ACET) und die Best Case Execution Time (BCET). Anschließend kann durch entsprechende Kombination der BB-Statistiken anhand des Programmablaufplans Rückschlüsse auf die Ausführungszeit des Programms gezogen werden.

Die Zerlegung eines Programms in BBs geschieht bereits automatisiert. Hierbei entsteht ein XML-Dokument mit Informationen über die einzelnen BBs des Programms, wie die Adressen der ersten und letzten Instruktionen. Darüber hinaus werden die BBs zu einem Flussgraph angeordnet, so dass sich mögliche Programmabläufe bestimmen lassen.

Ziel dieser Arbeit ist das Design und die Implementierung eines Software-Tools, das bestehende XML-Dokumente aufbereitet und eines Hardware-Moduls, welches unter Zuhilfenahme dieser aufbereiteten Informationen, die Ausführungszeit einzelner BBs misst.

Eine nachfolgende Arbeit wird auf diese Zeiten zurückgreifen und Statistiken über die Ausführungszeiten der einzelnen BBs erstellen.

Student: Tobias Schladt

Supervisor: Philip Gottschling

Time period: 04/15/2015 - 09/09/2015

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Inzwischen setzt die Xilinx Plattform bei fast allen IP-Komponenten auf AXI (Advanced eXtensible Interface Bus) als Peripheriebus. Der Bus verwendet zum Lesen und Schreiben einen Handshake und bietet die Möglichkeit von Burst-Transfers für schnelle Datenübertragungen. Um die Anbindung solcher vorgefertigter Module an die SpartanMC-Architektur zu vereinfachen, soll daher im Rahmen einer Bachelorarbeit ein AXI-Bus-Master implementiert werden. Dieser soll dann auch Einzug in die bestehende Entwicklungsumgebung für den SpartanMC erhalten.

Student: Frederik Lührs

Supervisor: Changgong Li

Time period: 10/01/2014 - 02/28/2015

Im Rahmen dieser Arbeit soll ein kompaktes Speicherlayout (z.B. durch Nutzung eines gemeinsamen Constant-Pools) für den Code-Memory eines Java-Prozessors entworfen werden. Dafür muss ein Werkzeug realisiert werden, welches die Klassendateien von Java laden kann und sie in eine passende, kompakte interne Darstellung umwandelt. Hierbei sollen alle symbolischen Referenzen einer Klassendatei während des Ladens aufgelöst und durch relative/absolute Adressen ersetzt werden (static binding). Dies hat zur Folge, dass alle referenzierten Klassen auch rekursiv geladen werden müssen. Nachdem alle Klassen eines Java Programms bereits komplett geladen und resolviert sind, sollen diese anhand des Speicherlayouts in eine binäre Datei exportiert werden, welche sich direkt auf das FPGA herunterladen lässt, in welchem der AMIDAR Prozessor implementiert wird.

Student: Ralf Kundel

Supervisor: Lukas Jung

Time period: 04/23/2015 - 08/14/2015

Student: Sven Himer

Supervisor: Changgong Li

Time period: 06/01/2015 - 11/01/2015

Im Rahmen dieser Arbeit soll ein Object-Heap auf AMIDAR-Basis für einen Java-Prozessor realisiert werden. Die Speicherung von Objekten und Arrays soll in externem DRAM-Speicher stattfinden. Dafür müssen die Speicherlayouts für normale Objekte und Array-Objekte neu entworfen werden, um alle im Java-Bytecode definierten Heap-Operationen unterstützen zu können. Außerdem muss hierbei auch eine effiziente Cache-Struktur berücksichtigt werden um den Zugriff auf den Heap möglichst zu beschleunigen.

Student: Sven Himer

Supervisor: Changgong Li

Time period: 04/20/2015 - 11/20/2015

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. In diesem Modell werden Instruktionen in eine Komposition von so genannten Tokens zerlegt, die dann an einzelne Funktionseinheiten verteilt werden. Die Funktionseinheiten koordinieren ihre Arbeit über die Daten, die sie produzieren oder konsumieren.

Ziel dieser Arbeit ist die Implementierung eines Ray-Tracers (Raytracing) mit Videoausgabe auf dem AMIDAR-Prozessor. Softwaremäßig soll dieser in Java 1.4 realisiert werden.

Damit sich die transformierten Bilder über einen DVI-Anschluss auf einem Bildschirm zeigen lassen, müssen verschiedene Peripherie-Module für den Wishbone-Bus realisiert werden (inkl. passender Java-API) implementiert werden. Schließlich muss ein existierender Ray-Tracer an diese Schnittstellen angepasst werden

Student: Sven Ströher

Supervisor: Lukas Jung

Time period: 04/03/2015 - 11/03/2015

Student: Markus Noll

Supervisor: Kris Heid

Time period: 12/01/2014 - 04/01/2015

Auf modernen FPGAs können mehrere dieser Kerne Platz finden. Die einzelnen Kerne können über FIFO basierte Kommunikationsstrukturen paarweise miteinander verbunden werden, um Daten untereinander auszutauschen. Bei einer großen Zahl gleichzeitig zu realisierender Verbindungen kann die paarweise Bereitstellung von FIFOs für jede Kommunikationsbeziehung zu einer relativ ineffizienten Ressourcennutzung führen.

Ziel der Arbeit ist es einen Verteiler (Dispatcher), respektive Konzentrator zu erstellen, der die Kommunikation zwischen den Rechenkernen bündelt. Dies soll zum einen die Verknüpfung der Rechenkerne vereinfachen und zum anderen den Hardwareaufwand verringern.

Student: Ramon Wirsch

Supervisor: Kris Heid

Time period: 10/13/2014 - 03/13/2015

Um die Funktionalität von Prozessoren sowie Debugging zu ermöglichen wird auf Prozessoren zusätzliche Hardware verwendet, die es ermöglicht den aktuellen Zustand des Prozessors und aller Register einzusehen. Hierfür benötigt der Prozessor Break-Point Instrunktion, die es ermöglichen einen Schappschuss des aktuellen Zustands auszulösen. In Break-/Watch-Point Registern wird dieser Zustand dann zwischengespeichert. In einem letzten Schritt geht es nun darum den Prozessorzustand für den Anwender anschaulich wiederzugeben. Hier ist es denkbar ein Mini-Monitor als Java-Anwendung aus dem Computer zu erstellen und die Informationen grafisch aufzubereiten.

Ziel dieser Arbeit ist es diese Funktionalität in den SpartanMC Prozessor zu integrieren.

Student: Carsten Heinz

Supervisor: Kris Heid

Time period: 02/16/2015 - 05/04/2015

Durch die außergewöhnlichen Bitbreite und den eigenen Befehlssatz bietet kein Compiler die Kompilierung von SpartanMC C-Programmen "Out of the Box" an. Aus diesem Grund wurde der Gnu Compiler Collection (GCC) angepasst.

Zum jetzigen Zeitpunkt unterstützt der angepasste Compiler allerdings noch keine vollständige Implementierung der Lib C. Diese ist erforderlich um alle Standard-Methoden beispielsweise zur Speicherverwaltung, mathematische Operationen oder Ein- und Ausgabe Funktionen zugänglich machen zu können.

Ziel dieser Arbeit ist es, die fehlenden Funktionen wie vom GCC gefordert für SpartanMC in die Lib C zu implementieren und somit für den Nutzer zugänglich zu machen.

Student: Lukas Boland

Supervisor: Kris Heid

Time period: 04/07/2015 - 09/07/2015

Der SpartanMC wurde, wie der Name nahe legt, auf Spartan3 FPGAs von Xilinx entwickelt. Implementiert und eingesetzt wurde er bisher auch auf den FPGA-Familien Spartan6 und Virtex5. Grundsätzlich lässt sich der Prozessorkern aber auch auf beliebigen anderen FPGA-Familien (insbesondere auch von anderen FPGA-Herstellern) verwenden.

In einer früheren Arbeit wurde bereits mit der Portierung des SpartanMC Core auf Lattice und Altera begonnen. In dieser Arbeit soll die Portierung der Peripherie Module in Angriff genommen und getestet werden. Des weiteren ist die Lattice Toolchain zu vervollständigen.

Als Test Plattform für die Portierung stehen DE0-Nano Boards mit Altera Cyclone IV FPGAs sowie ein LatticeECP3 Evaluation Board zur Verfügung.

Student: Felix Hübner

Supervisor: Boris Dreyer

Time period: 09/15/2015 - 12/15/2015

Das Fachgebiet Rechnersysteme bietet seit dem Sommersemester 2014 das Digitaltechnische Praktikum wieder an. Während des Digitaltechnischen Praktikums setzen sich Studenten mit dem MP3-Verfahren zum Kodieren und Dekodieren von Audio-Signalen intensiv auseinander und implementieren einen Teil der Dekodierungslogik. Zur effizienten Verarbeitung der MP3-Frames innerhalb des FPGAs geschieht diese mittels Festkommaarithmetik. Dies führt zu Rundungsfehlern mit entsprechender Auswirkung auf die Klangqualität.

Ziel dieser Arbeit ist die Implementierung eines MP3-Players zur Untersuchung der Korrelation zwischen Klangqualität und unterschiedlich präzisen Festkommadarstellungen. Hierzu soll der Player in C implementiert und die Genauigkeit der Festkommadarstellung parametrierbar gewählt werden können.

Master Theses

Student: Tajas Ruschke

Supervisor: Lukas Jung

Time period: 05/20/2015 - 11/20/2015

Im Rahmen dieser Arbeit soll ein Schedulingverfahren für das in AMIDAR verwendete generische CGRA-Modell entworfen und implementiert werden. Hierbei sind neben den bekannten Ressourcen-Beschränkungen insbesondere auch Routing-Beschränkungen durch die interne CGRA-Struktur zu beachten. Es soll möglich sein, diese Beschränkungen aus einer textuellen Beschreibung zu extrahieren.

Student: Dennis Wolf

Supervisor: Lukas Jung

Time period: 05/26/2015 - 11/26/2015

Im Rahmen dieser Arbeit soll nun ein CGRA für AMIDAR in Verilog entworfen werden. Der Aufbau der Processing Elements und deren Interconnect soll dabei generisch beschrieben werden. Es soll möglich sein, aus einer textuellen Beschreibung des CGRAs gültigen Verilog Code zu generieren. Konzepte zur Kommunikation zwischen dem AMIDAR Prozessor und dem CGRA sowie Mechanismen zur Steuerung des Programmablaufs müssen entworfen und umgesetzt werden.

Student: Christian Rose

Supervisor: Changgong Li

Time period: 05/01/2015 - 11/01/2015

Die erzeugten Beschreibungen werden mit Hilfe eines Parsers in eine Konfiguration für den Token Generator übersetzt. Bisher ist es allerdings nicht möglich Befehlssätze zu beschreiben deren Instruktionslänge ein Byte überschreitet, oder welche variable Befehlsbreiten enthalten.

Ziel dieser Arbeit soll es sein sowohl ADLA, als auch die ADLA-Tool-Chain so zu überarbeiten, das eine Unterstützung von Befehlssätzen mit den oben beschriebenen Charakteristika möglich ist. Weiterhin soll in der Beschreibungssprache eine Möglichkeit zur Modularisierung vorgesehen werden. Diese soll es erlauben die Beschreibung eines Token Generators auf mehrere Quellen zu verteilen.

Student: Christian Rose

Supervisor: Changgong Li

Time period: 05/01/2015 - 11/01/2015

Bisherige Arbeiten (www.amidar.de) haben gezeigt das ein deutliches Beschleunigungspotential für Applikationen im Bereich der eingebetteten Systeme besteht.

Der Token Generator ist eine wesentliche Komponente im AMIDAR Modell. Er verteilt die Mikroinstruktionen an alle Funktionseinheiten des Prozessors und sorgt so für die korrekte Abarbeitung von Maschinenbefehlen (hier Java Bytecode). Für die Simulation solcher Prozessoren konnte in früheren Versionen des AMIDAR-Simulators der Token Generator aus der Beschreibungssprache ADLA erzeugt werden. Im Rahmen dieser Arbeit soll zunächst der vorhandene ADLA-Compiler an die aktuellen Strukturen des Simulators angepasst werden. Im zweiten Schritt soll dann aus der ADLA Beschreibung ein Token Generator für eine FPGA Implmentierung eines AMIDAR-Prozessors erzeugt werden. Dieser Token Generator soll dabei unmittelbar auf den externen Speicher zugreifen, um sich Bytecode Befehle zu holen. Gegebenenfalls bietet sich hier der Einsatz eines Instruktions-Caches an.

Student: Christian Illy

Supervisor: Changgong Li

Time period: 05/01/2015 - 11/01/2015

Am Fachgebiet Rechnersysteme wird an adaptiven Prozessorstrukturen geforscht. Die Familie der AMIDAR Prozessoren basiert dabei auf einem Modell, welches an der Professur Mikrorechner der TU Dresden entwickelt wurde. Dieses Modell erlaubt es dem Prozessor zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. Hierzu zählen sowohl die Anpassung von Busstrukturen, als auch die Anpassung von bestehenden und die Synthese von neuen Funktionseinheiten.

Im Rahmen dieser Arbeit soll ein generischer Stack-Speicher auf AMIDAR-Basis für einen Java-Prozessor in Verilog realisiert werden. Aus diesem sollen dann spezielle Stack-Module leicht abgeleitet werden können, wie z.B. Method-Stack und Operand-Stack, welche alle vom Java-Bytecode, bzw. vom AMIDAR-Modell definierten Stack-Operationen unterstützen müssen.

Student: Christian Illy

Supervisor: Changgong Li

Time period: 05/01/2015 - 11/01/2015

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. In diesem Modell werden Instruktionen in eine Komposition von so genannten Tokens zerlegt, die dann an einzelne Funktionseinheiten verteilt werden. Die Funktionseinheiten koordinieren ihre Arbeit über die Daten, die sie produzieren oder konsumieren.

Ziel dieser Arbeit ist die Implementierung der Thread-Verwaltung in diesem AMIDAR-Prozessor. Zunächst soll ein Mechanismus zur Ausführung nativer Methoden entwickelt werden. Dieser soll allgemein gehalten und nicht speziell auf die Anforderungen der Thread-Verwaltung zugeschnitten sein.

In einem zweiten Schritt soll die Konzeption der zur Verwaltung von Threads notwendigen Strukturen erfolgen. Ein zentraler Bestandteil dieses Schrittes ist der Entwurf einer effektiven Verwaltung der Methodenstacks, Operandenstacks und der lokalen Variablen der einzelnen parallel ausgeführten Threads. Weiterhin wird ein Scheduler und damit verbunden eine Warteschlange benötigt.

Ein weiteres essentielles Ziel dieser Arbeit ist der Entwurf eines effizienten Mechanismus zur Realisierung verschiedener Synchronisationskonzepte. Diese können sowohl auf Monitoren, Semaphoren oder Mutexen beruhen. Die verschiedenen Varianten sind in Bezug auf ihre Realiserbarkeit im AMIDAR-Prozessor zu untersuchen. Die Entscheidung für eine spezielle Variante ist zu begründen.

Student: Jan Weber

Supervisor: Kris Heid

Time period: 04/05/2015 - 10/05/2015

Student: Muhammad Naveed Baig

Supervisor: Kris Heid

Time period: 03/01/2015 - 09/01/2015

Das bisherige SpartanMC-SoC-Kit ermöglicht bereits das komfortable Zusammenstellen eines SoC nach eigenen Wünschen über eine grafische Oberfläche. Jedoch muss der Nutzer Aus-/Eingänge der hinzugefügten Komponenten manuell verknüpfen und konfigurieren, was eine sehr zeitraubende und fehleranfällige Arbeit ist.

Durch diese Arbeit soll der Schritt der manuellen Konfiguration nahezu hinfällig werden. Hierzu sollen alle Komponenten mit Intelligenz in Form von ausführbaren LUA-Skripten in deren Modulbeschreibung ausgestattet werden. Durch diesen Schritt könnten sich die Komponenten beim hinzufügen selbst konfigurieren und beispielsweise bereits eindeutig zusammengehörige Ein-/Ausgänge miteinander verknüpfen. Um die neue Funktionalität dem Nutzer zur Verfügung zu stellen, müsste außerdem die bestehende grafische Oberfläche angepasst werden, um diese Skripte interpretieren zu können. Hierdurch würde diese Arbeit die SoC Konfiguration innerhalb von einem Bruchteil der bisherigen Zeit ermöglichen und außerdem die Komplexitätshürde erheblich senken.