Lecture "High-Level Synthesis"

Content

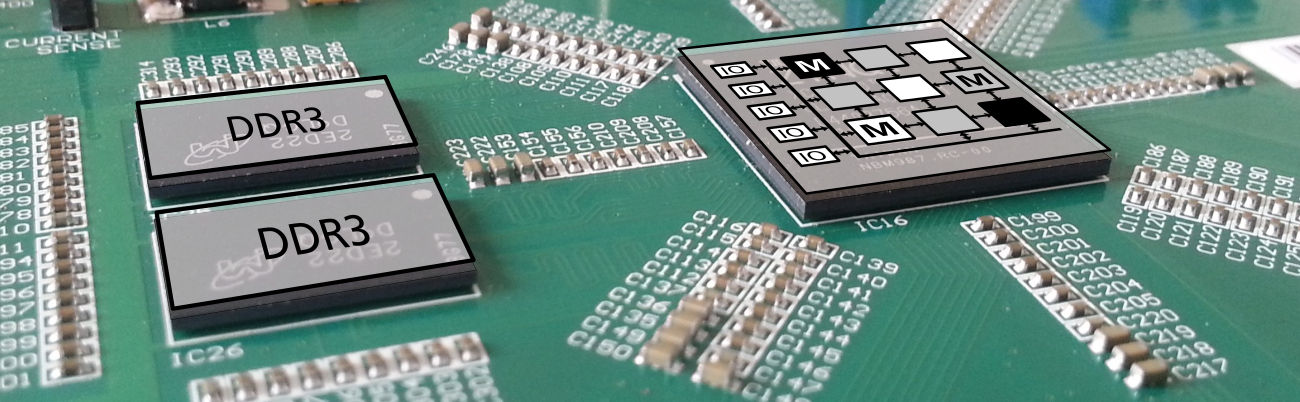

- Mapping of behavioral descriptions (e.g. in the form of program fragments) on FPGA and CGRA structures

- Sub-tasks allocation, scheduling, binding

- Exact or heuristic solutions

- Design principles of heuristic solutions

Organisation

| Typ: | Lecture (V2) |

| Date: | TUCaN |

| Room: | S3|06 053 |

| Begin: | 20.10.2025 |

| Lecturer: | Prof. Dr.-Ing. Christian Hochberger |

| CP: | see TUCaN |

| Cycle: | every winter semester |

| Language: | English |

Prerequisites

- Knowledge of hardware synthesis on the basis of at least one hardware description lan-guage is required (e.g. Reese/Thornton: Introduction to Logic Synthesis Using Verilog HDL oder Brown/Vranesic: Fundamentals of Digital Logic with VHDL Design).

- The student should have basic knowledge of at least one object oriented programming lan-guage, preferably Java