Bachelor-Arbeiten

Student*in: Simon Gütthoff

Betreuer*in: Dennis Wolf

Zeitraum: 03.04.2017 - 01.01.2018

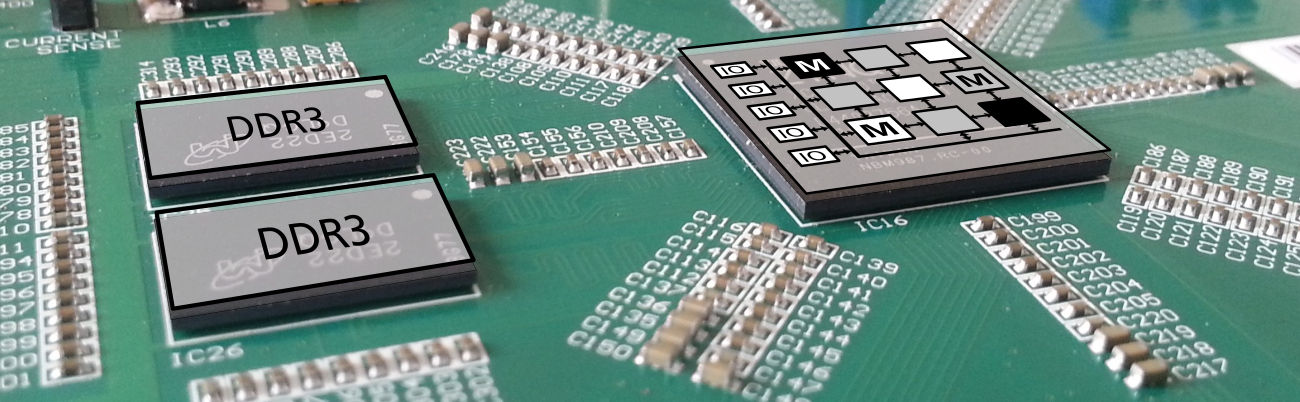

Ein Coarse Grained Reconfigurable Array (CGRA) ist eine Schaltung, die zumeist als Hardwarebeschleuniger eingesetzt wird. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel. Die Selektion an Operationen der einzelnen Rechenzellen, sowie deren Anzahl und Verbindung untereinander sind generisch und im Einzelfall entscheidend für die Laufzeit einzelner Applikationen.

Entsprechend mehrerer Beispielapplikationen kann ein CGRA für eine Anwendungsdomäne optimiert werden. Die Erzeugung einer optimalen CGRA Komposition ist dabei aufgrund der Komplexität nicht mehr möglich. In solchen Fällen werden heuristische Optimierungsverfahren genutzt. In diesem Fall finden sich zwei der drei relevanten Kosten in der möglichen Taktfrequenz und den benötigten Ressourcen einer CGRA Instanz. Da ein Syntheselauf allerdings im Stundenbereich liegen kann, muss eine Schätzung genutzt werden.

Im Rahmen dieser Arbeit soll ein Bibliotheks- basierter Schätzer entworfen werden, der die maximale Taktfrequenz und den Ressourcenverbrauch für eine Komposition auf einem FPGA bestimmt. Das Erstellen der Bibliothek für einzelne FPGA Typen soll im Laufe der Arbeit automatisiert werden.

Student*in: Evrard Simo

Betreuer*in: Lukas Jung

Zeitraum: 01.05.2018 - 31.07.2018

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren.

Es ist möglich Programmteile, die häufig ausgeführt werden, automatisch auf einen rekonfigurierbaren Baustein (Coarse Grained Reconfigurable Array, kurz CGRA) abzubilden, und somit zu beschleunigen. Dieser Vorgang wird als Hardware Synthese bezeichnet.

An der Universität of Wisconsin-Madison wird an einem ähnlichen Projekt namens DySER (Dynamically Specialized Execution Resources) geforscht. Ziel dieser Bachelorarbeit ist es, die Hardware Synthese mit DySER hinsichtlich Funktionsweise und Leistungsfähigkeit zu vergleichen.

Interessante Aspekte sind unter anderen welche Code-Teile auf Hardware abgebildet werden können, wie Kontrollfluss umgesetzt wird oder wie die Kommunikation zwischen Beschleuniger und Prozessor umgesetzt ist.

Student*in: Ho Thanh Tu Nguyen

Betreuer*in: Kris Heid

Zeitraum: 13.11.2017 - 13.04.2018

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Momentan wird daran gearbeitet hoch parallele Multiprozessor System-On-Chips (MPSoC) zu erstellen. Hierfür wird µStreams (ein eigens entwickeltes Parallelisierungs-Tool) genutzt. µStreams nimmt ein gewöhnliches sequenzielles Programm entgegen und parallelisiert dieses automatisch. Das erzeugte Many-Core System kommuniziert und synchronisiert sich über 1 zu 1, 1 zu N, N zu 1 Verbindungen, einen Router für Networks-On-Chip (NoC) und einen geteilten Speicher. Das resultierende MPSoC System ist dann eine Verarbeitungspipeline, ähnlich aktueller Prozessorpipelines, nur grob granularer arbeitend.

Je nach MPSoC Konfiguration werden auf dem FPGA unterschiedliche maximale Frequenzen erreicht, abhängig von Anzahl an Prozessoren, Periperie und Speicher. Die maximal erreichbare Frequenz gibt bei der Entscheidung zwischen mehreren realisierbaren MPSoC Konfigurationen möglicherweise den Ausschlag für oder gegen eine bestimmte Konfiguration. Leider ist momentan die Evaluation der maximalen Frequenz erst relativ weit am Ende des Design Prozesses möglich und geschieht erst nach einer Entscheidung für eine bestimmte Konfiguration. Dies ist für den Nutzer enorm Zeitaufwendig und verlangsamt die Findung einer optimalen Lösung.

Ziel dieser Arbeit soll es sein, eine Schätzfunktion für die maximal mögliche Frequenz einer gegebenen Konfiguration zu erstellen. Um herauszufinden welche Faktoren wie stark die Frequenz beeinflussen, sollen in dieser Arbeit verschiedene Konfigurationen systematisch gebaut und synthetisiert werden. Anschließend sollen die Erkenntnisse in einer Funktion in Form eine Java-Klasse bereitgestellt werden.

Student*in: Isabelle Bacher

Betreuer*in: Philip Gottschling

Zeitraum: 04.09.2017 - 19.01.2018

Oftmals benötigt man einen Kommunikationskanal zwischen einem Host-PC und dem am Fachgebiet Rechnersysteme entwickelten SpartanMC Softcore. Zur schnellen Datenübertragung eignet sich ein USB 3.0 Interface, da es Datenraten bis zu 5Gbit/s unterstützt. Derzeit steht allerdings nur eine USB 1.1 Schnittstelle zur Verfügung, deren Datenrate mit 12Mbit/s deutlich geringer ausfällt. Im Rahmen dieser Bachelorarbeit soll ein Peripherie-Modul weiterentwickelt werden, die über ein FTDI USB 3.0 Modul mit einem PC Daten austauschen kann. Mit diesem Modul lassen sich im FT245-Modus 32 Bit breite Worte bei einer maximalen Frequenz von 100Mhz übertragen.

Student*in: Lukas Schild

Betreuer*in: Kris Heid

Zeitraum: 01.05.2017 - 01.02.2018

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt. Ein in direkter Konkurrenz mit dem SpartanMC stehender SoC ist der Microblaze von Xilinx.

Um den Microblaze zu verwenden, muss der Nutzer die Konfiguration im Xilinx eigenen Konfigurationstool: Xilinx Platform Studio (XPS) manuell zusammenstellen. Um den SpartanMC konfigurieren und instantiieren zu können wurde jConfig entwickelt. jConfig bietet dem Nutzer generell die Möglichkeit beliebige Hardware zu instantiieren. Außerdem bietet es sehr gute Unterstützung um Komponenten aus einer sehr einfachen XML Beschreibung zu importieren. Über individuelle Skripte werden die Komponenten mit sehr wenig manuellem Aufwand konfiguriert und verkabelt. Der Nutzer muss im Gegensatz zum XPS kaum noch tätig werden. In jConfig befindet sich bereits sehr viele Peripheriekomponenten für SpartanMC.

Seit kurzem ist nun auch der Microblaze in jConfig instantiierbar. Allerdings steht und fällt die Verwendbarkeit eines SoC mit den verfügbaren Peripheriekomponenten und für Microblaze sind bisher erst UART und FSL Interconnects verfügbar. Daher sollen in dieser Arbeit mehr Peripheriekomponenten für den Microblaze über jConfig zugänglich gemacht werden. Hierzu müssen die Komponenten aus XPS ausgelesen und über eine Instantiierung in einem passenden Verilog Wrapper in jConfig verfügbar gemacht werden. Um die gewünschte automatisierte Konfiguration zu erreichen, müssen außerdem die Peripheriekomponenten um individuelle Skripte ergänzt werden. Anschließend sollten die Komponenten getestet werden. Bei den zu portierenden Komponenten handelt es sich um populäre Protokolle für Mikrocontroller wie: SPI, I2C, USB und AXI-Stream Interconnect für Multi-Core Systeme.

Student*in: Heiko Schüßler

Betreuer*in: Jakob Wenzel

Zeitraum: 22.06.2018 - 22.11.2018

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Der in den SpartanMC integrierte Debugging-Support nutzt zur Kommunikation mit dem Host-PC bisher eine UART-Schnittstelle. Auch für printf-Ausgaben wird eine UART-Schnittstelle benötigt. In Multicore-Systemen ist dieser Umstand problematisch: Jeder Core benötigt eine eigene UART-Verbindung, es existiert aber nur eine einzige Verbindung zum Host.

Ziel dieser Arbeit ist es, diese Situation zu verbessern. Es soll eine Kommunikationsstruktur erstellt werden, die es erlaubt, eine große Anzahl interner Ports mit dem Host-PC zu verbinden. Statt per UART soll dies aber per JTAG erfolgen, da diese Verbindung mit einem höheren Takt arbeiten kann.

Auf Host-PC-Seite müssen die zu einem Port zusammengeführten Daten wieder getrennt werden. Dabei muss eine eindeutige Zuordnung der Daten zu den Ports möglich sein. Hierzu soll ein Linux-Programm erstellt werden, das die Daten auf Pseudo-Geräte aufteilt. Dadurch ist der Zugriff von jedem Programm, das normale serielle Schnittstellen verwenden kann, möglich.

Student*in: Johannes Klöhn

Betreuer*in: Jakob Wenzel

Zeitraum: 11.04.2018 - 11.09.2018

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Als Programm- und Datenspeicher werden die Block-RAMs des FPGAs verwendet. Da diese gerade bei Many-Core-Systemen stark limitiert sind, ist es ratsam, einem Kern nicht mehr Block-RAMs zuzuteilen, als auch benötigt werden. Diese Anzahl genau zu ermitteln ist schwierig, da sich beispielsweise die Größe des Stack über die Laufzeit des Programms ändert. Ziel dieser Arbeit ist daher eine statische Analyse der Größe des benötigten Speichers eines Programms.

Die Größe von Programmcode und Daten sind statisch bekannt. Herausforderung dieser Arbeit ist hingegen die Bestimmung der maximalen Stackgröße. Bei der Kompilierung kann GCC optional die Stackgrößen aller Funktionen in eine separate Datei ausgeben. Die Größen sind dabei nur die der Funktionen selber und enthalten nicht die der von ihnen aufgerufenen Funktionen.

Aus dem fertig gelinkten Programm oder aus den dazugehörigen Debug-Infos soll anschließend rekonstruiert werden, welche Funktionen aus einer Funktion heraus aufgerufen werden. Zusammen mit dem Speicherbedarf der einzelnen Funktionen lässt sich dann eine Worst-Case-Stackgröße ermitteln.

Student*in: Jonas Diegelmann

Betreuer*in: Kris Heid

Zeitraum: 06.11.2017 - 06.04.2018

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Momentan wird daran gearbeitet hoch parallele Multiprozessor System-On-Chips (MPSoC) zu erstellen. Hierfür wird µStreams (ein eigens entwickeltes Parallelisierungs-Tool) genutzt. µStreams nimmt ein gewöhnliches sequenzielles Programm entgegen und parallelisiert dies automatisch. Das erzeugte Many-Core System kommuniziert und synchronisiert sich über 1 zu 1, 1 zu N, N zu 1 Verbindungen, einen Router für Networks-On-Chip (NoC) und einen geteilten Speicher. Das resultierende MPSoC System ist dann eine Verarbeitungspipeline, ähnlich aktueller Prozessorpipelines, nur grob granularer arbeitend.

µStreams ist mit AutoStreams mittlerweile in der Lage, anhand eines Performance-Profils ein Programm in eine (beliebige) Anzahl an Threads aufzuteilen. Hierbei wird lediglich eine Pipeline mit 1:1 Verbindungen aufgebaut. Dies ist die einfachste Variante einer Aufteilung. µStreams besitzt allerdings momentan weitaus mehr ungenutzte Parallelsierungsmechnismen:

- Scheifen (welche möglicherweise die kritische Pipelinestufe bilden) weiter aufteilen, um Aufteilungspunkte besser platzieren zu können und eine ausgewogene Pipeline zu bekommen.

- Bei einer Entscheidung zwischen mehreren möglichen Aufteilungen, den geschätzten Ressourcenverbrauch auf dem FPGA bzw. die maximal mögliche Frequenz mit einzubeziehen.

- Nutzung des

replicateKonstrunkts aus µStreams, um kritische Pipelinestufen quasi Superskalar aufzubauen und damit zu entlasten.

Ziel dieser Arbeit soll es daher sein, die bisher ungenutzten Parallelisierungsmechnismen zu integrieren, um das volle Potential von µStreams auszunutzen und optimal zu unterstützen.

Master-Arbeiten

Student*in: Abhishek Sirsikar

Betreuer*in: Tajas Ruschke

Zeitraum: 30.09.2017 - 09.04.2018

Am Fachgebiet Rechnersysteme wird momentan an einer CGRA-Architektur geforscht, die zur Beschleunigung des Programmablaufs verwendet werden soll.

Damit ein Programmteil auf das CGRA abgebildet werden kann, muss ein Scheduler die Problemgraphen auf die Zielhardware abbilden. Dabei müssen verschiedene Abhängigkeiten berücksichtigt werden, um den korrekten Programmablauf zu gewährleisten. Eine besondere Herausforderung besteht in der Berücksichtigung der Datenlokalität und der Verbindungseinschränkungen. Bei der Abbildung des Graphen rückwärts vorzugehen verspricht eine Vereinfachung bei der Lösung des Routingproblems. Als alternative zur bisher umgesetzten spekulativen Operationsausführung soll eine prädizierte Ausführung angewendet werden.Ziel dieser Arbeit ist das Design und die Implementierung eines Scheduler-Verfahrens, welches den Graphen in umgekehrter Reihenfolge bearbeitet und dabei alle Einschränkungen berücksichtigt.

Student*in: Blandine Rivière

Betreuer*in: Johanna Rohde

Zeitraum: 03.04.2018 - 02.10.2018

Ein Forschungsprojekt am Fachgebiet Rechnersysteme der TU Darmstadt befasst sich mit der Entwicklung des PIRANHA GCC Plugins zur automatischen Erzeugung von Hardwarebeschleunigern. Das Plugin führt dazu eine statische Programmanalyse des Programmcodes durch und wählt eigenständig die Schleifen aus, die voraussichtlich die größte Ausführungszeit benötigen. Anschließend wird deren Funktionalität mit Hilfe einer High Level Synthese als Hardwarebeschleuniger implementiert. Der Zugriff der Beschleuniger auf den Datenspeicher kann wahlweise direkt oder über ein Cachesystem erfolgen.

Der verfolgte Ansatz ist unabhängig vom Prozessor, an welchen die Beschleuniger als Peripheriekomponente angeschlossen werden. Gegenwärtig steht dafür vor allem der SpartanMC des gleichnamigen SoC-Kits zur Verfügung.

Der MicroBlaze ist ein 32-Bit RISC Softcore Prozessor entwickelt von Xilinx. Er bietet zahlreiche Konfigurationsmöglichkeiten wie z.B. die Anzahl der Pipelinestufen, zusätzliche arithmetische Einheiten und optionale Caches für Daten und Instruktionen.

Ziel dieser Arbeit ist es, die von PIRANHA unterstützten Prozessoren um den MicroBlaze von Xilinx zu erweitern. Dabei ist insbesondere auch das vorhandene Cachesystem an den MicroBlaze anzupassen.

Student*in: Tim Burkert

Betreuer*in: Changgong Li

Zeitraum: 16.04.2018 - 15.10.2018

Coarse Grained Reconfigurable Arrays (CGRA) sind Schaltungen, die zumeist als Hardwarebeschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel.

Problematisch bei fast allen CGRAs, die nicht direkt in einen Prozessor integriert sind, ist der vergleichsweise hohe Aufwand auf Daten der Anwendung zuzugreifen oder den Konfigurationsspeicher zu beschreiben. Um die Ausführungsdauer dieses Vorgangs zu reduzieren und die Kommunikation mit dem zugehörigen Prozessor zu gewährleisten ist eine PCIe-Schnittstelle auf Seiten des Host vorgesehen.

Im Rahmen dieser Arbeit soll ein vorhandenes CGRA mit einer PCIe-Schnittstelle versehen werden, welche die Kommunikationsschnittstelle zwischen Host und CGRA bildet und alle eingehenden Daten und Adressen entsprechend einer generischen CGRA Architektur passend aufarbeitet, bzw. die vom CGRA benötigten Daten in System konformer Weise aus dem Speicher des Host holt.

Student*in: Marek Völker

Betreuer*in: Changgong Li

Zeitraum: 01.05.2018 - 31.10.2018

Coarse Grained Reconfigurable Arrays (CGRA) sind Schaltungen, die zumeist als Hardwarebeschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel.

Ziel der Arbeit ist die Anpassung der bestehenden CGRA-Architektur an machine-learning Anwendungen. Bei diesen Anwendungen genügen häufig Festkommadarstellungen mit 32 oder 16 Bit Genauigkeit für die Berechnung. Daher ist es erforderlich entsprechende Rechenwerke bereitzustellen und gegebenenfalls zwei 16-bit Operationen zu einer kombinierten Operation zusammenzufassen. Je nach Ausgangsproblem kann es nötig werden swap-Operationen bereitzustellen.

Projektseminare Bachelor

Student*in: Ali Al Hannawi

Betreuer*in: Johanna Rohde

Zeitraum: 14.10.2017 - 14.03.2018

Nur für Projektseminar "Rekonfigurierbare Systeme" im Master

Das SpartanMC SoC Kit ist eine Toolchain zur Erzeugung von FPGA basierten Systemen. Zentraler Bestandteil ist ein Softcore, der durch verschiedene Hardwarekomponenten erweitert und mit Hilfe der Toolchain programmiert werden kann. Ein Forschungsprojekt innerhalb des SpartanMC SoC Kit befasst sich mit der Entwicklung eines GCC Plugins zur automatischen Erzeugung von Hardwarebeschleunigern. Das Plugin führt dazu eine statische Programmanalyse des Programmcodes durch und wählt eigenständig die Schleifen aus, die voraussichtlich die größte Ausführungszeit benötigen. Anschließend wird deren Funktionalität mit Hilfe einer High Level Synthese als Hardwarebeschleuniger implementiert.

Um die Menge an Instruktionen, die parallel ausgeführt werden können, zu erhöhen, kann es sinnvoll sein die innersten Schleifen abzurollen. Dafür stellt der GCC eine Transformation bereit, der eine Analyse vorausgeht, die bestimmen soll, ob eine solche Transformation im Hinblick auf Geschwindigkeit und Größe des Programmcodes sinnvoll ist. Für die High-Level-Synthese gelten jedoch andere Rahmenbedingungen, so dass die Analyse zu einem für diesen Zweck ungeeignetem Ergebnis kommt.

Teil dieser Aufgabe ist es, zu Analysieren in wie weit die vom GCC bereit gestellten Transformationen und Analysen für die Entwicklung eines Loop Unrolling dienlich sind. Anschließend soll ein Loop Unrolling ggf. auf Basis der vom GCC bereitgestellten Methoden implementiert werden.

Hiwi-Stellen

Student*in: Julian Käuser und Simon Gütthoff

Betreuer*in: Dennis Wolf und Tajas Ruschke

Zeitraum: 01.09.2017 - 28.03.2018

Wir suchen im Rahmen des Projektes Ultrasynth zwei Hilfswissenschaftler. Ihr sollt in Zusammenarbeit regelungstechnische Anwendungen auf CGRAs auf mehreren Ebenen simulieren. Es sollen eine High-Level Simulation und eine Simulation in ModelSim durchgeführt und abgeglichen werden. So können Fehler sowohl im Scheduling, als auch in der Hardware, erkannt und deren Quelle gefunden werden.

Bewerbungen sind nicht als Team erforderlich. Logischerweise teilen sich die Aufgabenbereiche auf die zwei Simulationen auf. Für die High-Level Simulation sollte der Inhalt der Vorlesung High-Level Synthese bekannt sein. Für die HDL Simulation werden gute Kenntnisse über (System-)Verilog vorausgesetzt. Außerdem wird Erfahrung mit Java bei beiden Anstellungen erwarten. Eine Vergütung von 36h pro Monat bis voraussichtlich Februar ist angesetzt.