Bachelor-Arbeiten

Student*in: Julian Käuser

Betreuer*in: Dennis Wolf

Zeitraum: 20.12.2016 - 20.02.2017

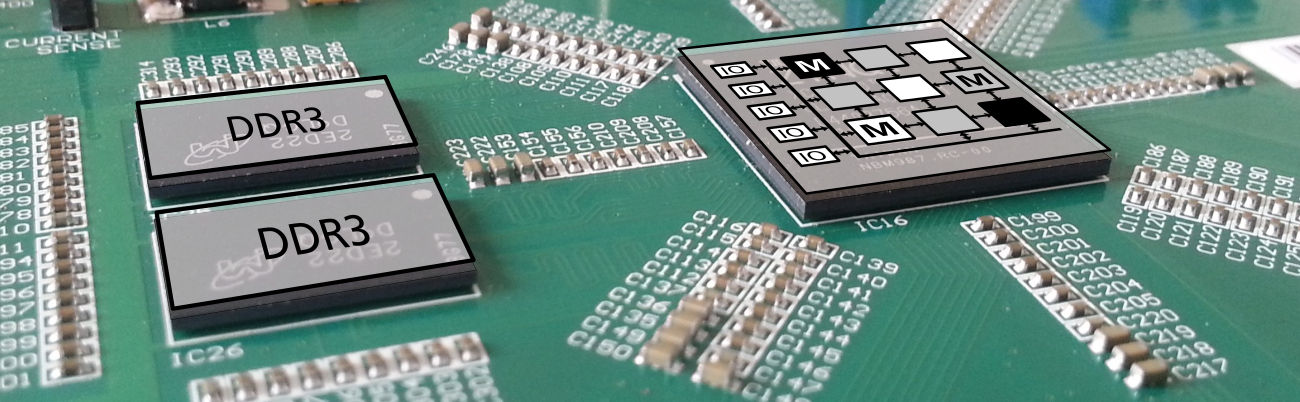

Coarse Grained Reconfigurable Arrays (CGRA) sind Schaltungen, die zumeist als Hardware-Beschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel. Das Operationssprektrum der einzelnen Rechenzellen sowie die Verbindung untereinander sind generisch und im Einzelfall entscheidend für die Laufzeit einzelner Applikationen.

In dem Projekt "Ultrasynth" soll entsprechend mehrerer Beispielapplikationen aus einer Anwendungsdomäne ein CGRA für diese Domäne automatisiert erstellt und implementiert werden. Die Erzeugung einer optimalen CGRA Komposition (beispielsweise die Anzahl an Rechenzellen und deren Operationsspektrum) ist dabei aufgrund der Komplexität nicht mehr möglich. In solchen Fällen werden Heuristiken genutzt, die darauf setzen ein nicht optimales aber ausreichend gutes Ergebnis zu liefern.

In dieser Arbeit sollen zunächst Charakteristika/Attribute aus exemplarischen Beispielanwendungen extrahiert werden. Darauf basierend soll mit einem konstruktiven Verfahren ein passendes CGRA modelliert werden.

Student*in: Marcel Heinlein

Betreuer*in: Dennis Wolf

Zeitraum: 20.12.2016 - 20.03.2017

CGRAs sind konfigurierbare Logik-Bausteine, die besonders geeignet sind, um rechenintensive Programmteile zu realisieren. Das Fachgebiet Rechnersysteme forscht seit geraumer Zeit auf diesem Gebiet. Nun sollen CGRAs auch in beliebige Rechnersysteme integriert werden.

Problematisch bei fast allen CGRAs, die nicht direkt in einen Prozessor integriert sind, ist der vergleichsweise hohe Aufwand den Konfigurationsspeicher zu beschreiben. Um die Ausführungsdauer dieses Vorgangs zu reduzieren und die Kommunikation mit dem zugehörigen Prozessor zu gewährleisten ist eine AXI-Slave Schnitstelle auf Seiten des CGRAs vorgesehen.

Im Rahmen dieser Arbeit soll diese AXI-Slave Schnittstelle entworfen werden, die die Kommunikationsschnittstelle zu einem Prozessor bildet und alle eingehenden Daten und Adressen entsprechend einer generischen CGRA Architektur passend aufarbeitet.

Student*in: Felix Retsch

Betreuer*in: Dennis Wolf

Zeitraum: 14.02.2017 - 14.02.2017

Coarse Grained Reconfigurable Arrays (CGRA) sind Schaltungen, die zumeist als Hardwarebeschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel. Das Operationsspektrum der einzelnen Rechenzellen, sowie die Verbindung untereinander, sind generisch und im Einzelfall entscheidend für die Laufzeit einzelner Applikationen.

In dem Projekt "UltraSynth" soll entsprechend mehrerer Beispielapplikationen ein CGRA für die entsprechende Anwendungsdomäne automatisiert erstellt und implementiert werden. Die Erzeugung einer optimalen CGRA Komposition (bzgl. der Anzahl an Rechenzellen und deren Operationsspektrums) ist dabei aufgrund der Komplexität nicht mehr möglich. In solchen Fällen werden Heuristiken genutzt, die darauf setzen, ein nicht zwingend optimales aber ausreichend gutes Ergebnis zu liefern. Für das vorliegende Optimierungsproblem kann die Heuristik "Simluated Annealing" genutzt werden.

Im Rahmen dieser Arbeit soll eine Version des Simulated Annealing implementiert werden. Dieses soll zur Findung einer möglichst guten Komposition für einen bestimmten Anwendungsbereich genutzt werden. Der Anwendungsbereich wird durch gegebene Applikationen definiert. Herausforderungen bestehen in der grundlegenden Parametrisierung des Algorithmus' sowie der Superposition oder Aggregation der Applikationen. In einem weiteren Schritt soll untersucht werden, ob entsprechend der Applikationen eine automatische Parametrisierung des Algorithmus' die Qualität gehoben und die Laufzeit gesenkt werden kann.

Student*in: Ludwig Meysel

Betreuer*in: Philip Gottschling

Zeitraum: 01.12.2016 - 28.02.2017

Ein Teilaspekt der Generierung von schnell rekonfigurierbaren Datenpfaden umfasst die automatische Überlagerung und anschließende Synthese von Datenflussgraphen. Damit wird erreicht, dass verschiedene Aufgaben in einem konfigurierbaren Verilog-Modul implementiert werden können. Um möglichst effiziente Module zu entwerfen, lassen sich definierte Strukturen innerhalb eines Datenflussgraphen zu atomaren Operationen zusammenfassen.

Viele der theoretisch möglichen Strukturen treten in echten Beispielen nur sehr selten oder sogar gar nicht auf. Um keine unnötige Arbeit in deren Optimierung zu investieren, sind Kenntnisse über die Gemeinsamkeiten von Datenflussgraphen und häufig auftretende Teilstrukturen hilfreich.

Student*in: Michael Meister

Betreuer*in: Lukas Jung

Zeitraum: 15.09.2017 - 15.12.2017

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. In diesem Modell werden Instruktionen in eine Komposition von sogenannten Tokens zerlegt, die dann an einzelne Funktionseinheiten verteilt werden. Die Funktionseinheiten koordinieren ihre Arbeit über die Daten, die sie produzieren oder konsumieren.

Um Java-Code auf diesem Prozessor ausführen zu können, müssen die Quelldateien zunächst kompiliert werden. Die dadurch erzeugten class-Dateien enthalten Java Bytecode und müssen anschließend mit Hilfe des AXT-Converters in ein Amidar-Excutable (AXT) umgewandelt werden. Eine AXT-Datei enthält dabei immer den Bytecode aller benötigten Java Klassen (leicht modifiziert) sowie benötigte Konstanten.

Derzeit wird sowohl vom Prozessor als auch vom AXT-Converter nur Java Version 1.4 unterstützt.

Im Zuge dieser Arbeit soll zunächst untersucht werden, worin die Unterschiede zwischen Java Version 1.4 sowie der aktuellen Version 8 auf Klassen-Ebene bestehen. Anschließend sollen Prozessor und AXT-Converter erweitert werden, sodass Java Version 8 unterstützt wird

Zusätzlich dazu müssen zugehörige API Klassen sowie der AMIDAR-Simulator ebenfalls erweitert werden.

Student*in: Lars Stein

Betreuer*in: Dennis Wolf

Zeitraum: 22.05.2017 - 21.08.2017

Am Fachgebiet Rechnersysteme wurde das Modell eines adaptiven Prozessors entwickelt (AMIDAR). Dieses Modell erlaubt es zur Laufzeit auf spezifische Anforderungen einer Applikation zu reagieren. Dazu zählt die Erkennung von rechenintensiven und wiederkehrenden Schleifen und deren Abbildung auf ein Coarse Grained Reconfigruable Array (CGRA). Ein CGRA ist ein Set aus Rechenzellen, die Instruktionssequenzen massiv parallel verarbeiten können. 2015 wurde hierfür eine generische CGRA Architektur implementiert. Mittels eines Generators können beliebige CGRA Instanzen in Verilog erzeugt werden, ohne dabei den Verilog Code manuell anpassen zu müssen. Die Architektur beherrscht zum jetzigen Zeitpunkt Arithmetik und Kontrollflussoperationen auf Basis von Festkommadarstellung. Um ohne Einschränkung relevante Code-Sequenzen abbilden zu können, ist es allerdings notwendig auch Gleitkommaberechnungen durchführen zu können.

Daher soll im Rahmen dieser Arbeit das CGRA um Gleitkommaoperationen und Datentypkonvertierungen erweitert werden. Dabei gilt es im ersten Schritt auch eine strategisch sinnvolle Auswahl an Implementierungen zu treffen. Neben der generischen Implementierung soll sich die Arbeit auf ausführliche Tests und die Verifikation durch Eigenschaftsnachweise (Property Checking) mit System Verilog Assertions konzentrieren.

Student*in: Adrian Weber

Betreuer*in: Lukas Jung

Zeitraum: 25.11.2016 - 24.04.2017

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren.

Es ist möglich Programmteile, die häufig ausgeführt werden, automatisch auf einen rekonfigurierbaren Baustein (Coarse Grained Reconfigurable Array, kurz CGRA) abzubilden, und somit zu beschleunigen. Dieser Vorgang wird als Hardware Synthese bezeichnet.

Um herauszufinden, welche Programmteile häufig ausgeführt werden, kann beispielsweise der Quellcode vor der Ausführung analysiert werden. Dies führt aber meist nicht zu verlässlichen Ergebnissen, da der Ablauf eines Programms oftmals von den Eingabedaten abhängt und daher erst zur Laufzeit festgelegt wird.

Deshalb soll im Prozessor ein Profiler implementiert werden, der die Ausführung eines Programms im laufenden Betrieb analysiert und ein Profil erstellt, aus dem ersichtlich ist, welche Schleifen im Programm besonders oft ausgeführt werden

(nähere Infos hier).

Da Programme, die auf dem AMIDAR-Prozessor ausgeführt werden, Zugang zu diesen Daten haben müssen, muss der Profiler auch als Peripherie-Gerät in den Prozessor eingebunden werden.

Student*in: Thorsten Melbaum

Betreuer*in: Jakob Wenzel

Zeitraum: 20.06.2017 - 20.09.2017

Das SpartanMC SoC-Kit ist eine Werkzeugkette und ein Satz von Soft- und Hardware-Komponenten, die Anwendern erlauben, ein anwendungsspezifisches SoC zu konstruieren, ohne selbst Spezialist für FPGAs zu sein. Um nicht für jede Änderung der Systemkonfiguration ein komplett neues System synthetisieren zu müssen, wurde RapidSoC erstellt. Dieses Werkzeug erlaubt es, vorab Module des SoC-Kit in partielle FPGA-Konfigurationen zu verwandeln. Bei Verwendung müssen diese dann nur noch zusammengefügt werden. Bei der Modulgenerierung werden Platzierungs-Constraints verwendet, um kompakte, rechteckige Module zu erzeugen.

Die Erstellung der Platzierungs-Constraints ist noch nicht automatisiert. Bisher können Benutzer aus einem Satz von fertigen Constraints auswählen, oder sie selbst erzeugen. Ziel dieser Arbeit ist die Automatisierung dieses Schritts. Nach dem Technologie-Mapping wird von den Hersteller-Tools eine Statistik über die Ressourcenverwendung des Moduls erzeugt. Aus dieser Statistik sollen passende Constraints erzeugt werden. Dabei müssen selten vorkommende Ressourcen wie Block-RAMS oder DSP-Blöcke speziell berücksichtigt werden.

Bei der Modul-Synthese wird jeder Port des Moduls an ein FPGA-Pin angeschlossen. Die Auswahl dieser Pins erfolgt bisher zufällig. Im Rahmen dieser Arbeit soll dafür ein besserer Ansatz gefunden werden.

Student*in: Andre Miebes

Betreuer*in: Kris Heid

Zeitraum: 18.10.2016 - 18.03.2017

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Zur Kommunikation mehrerer Prozessorkerne untereinander wurden bereits spezielle Schaltungen in SpartanMC integriert, welche eine 1-1 oder 1-N bzw. N-1 Kommunikation ermöglichen. Bei der Kommunikation der Kerne untereinander ist eine entsprechend hohe Bandbreite und niedrige Latenz essenziell. Alle bisherigen Implementierungen benötigen jedoch den Prozessor, um Daten von dem Hauptspeicher in den Peripherieadressbereich zu kopieren. Die Kommunikation erreicht hierbei einen akzeptablen Durchsatz, jedoch ist der Prozessor ausschließlich mit dem Kopieren beschäftigt und kann seinen eigentlichen Zweck (die Berechnung der Daten) nicht verfolgen.

Ziel dieser Arbeit ist daher eine Variante der Prozessorkommunikation zu entwickeln, welche über DMA arbeitet, um den Prozessor zu entlasten. Anstelle einzelner Datenwerte müsste der Prozessor lediglich die Startadresse der Daten übergeben, das stupide Kopieren würde die Peripherie erledigen.

Student*in: Tobias Averhage

Betreuer*in: Jakob Wenzel

Zeitraum: 20.02.2017 - 20.07.2017

Das SpartanMC SoC-Kit ist eine Werkzeugkette und ein Satz von Soft- und Hardware-Komponenten, die Anwendern erlauben, ein anwendungsspezifisches SoC zu konstruieren, ohne selbst Spezialist für FPGAs zu sein. Um nicht für jede Änderung der Systemkonfiguration ein komplett neues System synthetisieren zu müssen, wurde RapidSoC erstellt. Dieses Werkzeug erlaubt es, vorab Module des SoC-Kit in partielle FPGA-Konfigurationen zu verwandeln. Bei Verwendung müssen diese dann nur noch zusammengefügt werden. Bei der Modulgenerierung werden Platzierungs-Constraints verwendet, um kompakte, rechteckige Module zu erzeugen.

Diese Platzierungs-Constraints legen auch das Verhältnis von Höhe zu Breite der Module fest. Für verschiedene Kombinationen von Modulen können jedoch unterschiedliche Seitenverhältnisse sinnvoll sein. Ziel dieser Arbeit ist daher die Unterstützung verschiedener Versionen der Module. Da die Auswahl der zu verwendenden Version erst bei der Platzierung getroffen wird, müssen Informationen über die verwendeten Ressourcen schon vorher verfügbar sein, ohne jedoch das komplette Modul laden zu müssen. Daher soll ein Dateiformats zur Speicherung der fertigen Module entwickelt werden.

Student*in: Dominik Lorych

Betreuer*in: Kris Heid

Zeitraum: 25.04.2017 - 25.09.2017

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Momentan wird daran gearbeitet hoch parallele Multiprozessor System-On-Chips (MPSoC) zu erstellen. Hierfür wird µStreams (ein eigens entwickeltes Parallelisierungs-Tool) genutzt. µStreams nimmt ein gewöhnliches sequenzielles Programm entgegen und parallelisiert dies automatisch. Das erzeugte Many-Core System kommuniziert und synchronisiert sich über 1 zu 1, 1 zu N, N zu 1 Verbindungen, einen Router für Networks-On-Chip (NoC) und einen geteilten Speicher. Das resultierende MPSoC System ist dann eine Verarbeitungspipeline, ähnlich aktueller Prozessorpipelines, nur grob granularer arbeitend.

µStreams ist derzeit in der Lage mehrere Anweisungen, Schleifen oder komplette Funktionen auf einen Task abzubilden. Eine Analyse förderte jedoch zutage, dass einzelne Schleifen oft eine erhebliche Ausführungszeit besitzen, was zum kritischen Schritt in der MPSoC Verarbeitungspipeline werden kann. µStreams besitzt momentan noch keine Automatismen, um diese Schleifen aufzubrechen und noch weiter zu parallelisieren.

Daher soll in dieser Arbeit in µStreams Loop Tiling eingebaut werden. Hierdurch soll beispielsweise eine Schleife, welche zehn Durchläufe besitzt in zwei Schleifen zu je fünf Durchläufen transformiert werden. µStreams ist jetzt in der Lage beide Schleifen auf je einen Task zu packen und somit die Schleifen mit ca. doppelt so hohem Durchsatz auszuführen. Schleifen mit sehr vielen Durchläufen sind somit fast beliebig parallelisierbar.

Die Komplexität beim Loop Tiling liegt allerdings darin, die Grenzen einer Schleife (Start/Abbruchbedingung/Schrittweite) korrekt zu analysieren, um eine Aufteilung in gleich große Teile zu gewährleisten.

Master-Arbeiten

Student*in: Laleh Janipour

Betreuer*in: Tajas Ruschke

Zeitraum: 16.08.2016 - 16.02.2017

Am Fachgebiet Rechnersysteme wird momentan an einer CGRA-Architektur geforscht, die zur Beschleunigung des Programmablaufs verwendet werden soll.

Damit ein Programmteil auf das CGRA abgebildet werden kann, muss ein Scheduler die Problemgraphen auf die Ziel-Hardware abbilden. Dabei müssen verschiedene Abhängigkeiten berücksichtigt werden, um den korrekten Programmablauf zu gewährleisten. Die Erstellung der Problemgraphen geschieht bisher aus Java Bytecode. Zur Demonstration und zum Test weiterer Benchmarks ist eine Generierung von Graphen aus C-Code wünschenswert.

Ziel dieser Arbeit ist das Design und die Implementierung eines Graphgenerators, welcher Kontroll- und Datenflussinformationen sowie die ausgeführten Operationen in das am Fachgebiet verwendete Graphformat überführt. Dabei sollen auch einfache Schleifen übergreifende Abhängigkeiten berücksichtigt werden.

Student*in: Sebastian Focke

Betreuer*in: Tajas Ruschke

Zeitraum: 06.02.2017 - 07.08.2017

Student*in: David Winter

Betreuer*in: Tajas Ruschke

Zeitraum: 19.12.2016 - 19.06.2017

Am Fachgebiet Rechnersysteme wird momentan an einer CGRA-Architektur geforscht, die zur Beschleunigung des Programmablaufs verwendet werden soll.

Damit ein Programmteil auf das CGRA abgebildet werden kann, muss ein Scheduler die Problemgraphen auf die Zielhardware abbilden. Dabei müssen verschiedene Abhängigkeiten berücksichtigt werden, um den korrekten Programmablauf zu gewährleisten. Eine besondere Herausforderung besteht in der Berücksichtigung der Datenlokalität und der Verbindungseinschränkungen. Ein iterativer Ansatz verspricht Verbesserungen in der Ergebnisqualität.Ziel dieser Arbeit ist das Design und die Implementierung eines Scheduling-Verfahrens, welches das Problem durch einen iterativen Ansatz löst. Dabei sollen Erkenntnisse aus vorhergehenden Scheduling-Läufen in die nächste Iteration einfließen.

Student*in: Ashkan Ashooripour Moghadam

Betreuer*in: Dennis Wolf

Zeitraum: 10.10.2016 - 09.04.2017

Ein Coarse Grained Reconfigurable Array (CGRA) ist eine Schaltung, die zumeist als Hardwarebeschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel. Das Operationsspektrum der einzelnen Rechenzellen sowie die Verbindung untereinander sind generisch und im Einzelfall entscheidend für die Laufzeit einzelner Applikationen.

In dem Projekt "UltraSynth" soll entsprechend mehrerer Beispielapplikationen ein CGRA für die entsprechende Anwendungsdomäne automatisiert erstellt und implementiert werden. Die Erzeugung einer optimalen CGRA Komposition (bzgl. der Anzahl an Rechenzellen und deren Operationsspektrums) ist dabei aufgrund der Komplexität nicht mehr möglich. In solchen Fällen werden Heuristiken genutzt, die darauf setzen ein nicht zwingend optimales aber ausreichend gutes Ergebnis zu liefern. Diese Heuristiken benötigen mindestens eine Kostenfunktionen. In diesem Fall finden sich zwei der drei relevanten Kosten in der möglichen Taktfrequenz und den benötigten Ressourcen einer CGRA Instanz. Da ein Synthesevorgang einer CGRA Beschreibung im Minuten- oder Stundenbereich liegen kann, wurde ein neuronales Netz entwickelt, das beide Kosten schätzt. Dieses Erstellen und Anlernen des Netzes wurde bereits automatisiert

Im Rahmen dieser Arbeit soll in Kooperation mit dem Fachgebiet "Regelungsmethoden und Robotik" das neuronale Netz überarbeitet werden. Dabei gilt es nicht nur die Ergebnisqualität zu verbessern, sondern auch den Automatismus zur Erstellung eines Netzes in seiner Anwendbarkeit auf ganze Technologiefamilien zu erweitern. Ein möglicher Ansatz ist der Einsatz eines evolutionären Algorithmus' zur Findung einer gut geeigneten Topologie des Netzes.

Student*in: Raphael Nißl

Betreuer*in: Philip Gottschling

Zeitraum: 01.09.2016 - 28.02.2017

Ein Teilaspekt des CONIRAS-Projekts umfasst die automatische Überlagerung und anschließende Synthese von Datenflussgraphen. Damit wird erreicht, dass verschiedene Aufgaben in einem konfigurierbaren Verilog-Modul implementiert werden können. Um danach ein bestimmtes Problem auf die bereits synthetisierte Hardware abbilden zu können, muss entsprechend der korrekte Pfad durch den überlagerten Datenflussgraph gefunden werden. Damit reduziert sich die Wartezeit beim Wechsel zwischen Aufgaben oder einzelnen Werten innerhalb einer Aufgabe von Minuten (Syntheseprozess) auf Sekundenbruchteile.

In der derzeitigen Implementierung der Superposition lassen sich mindestens alle Ausgangsprobleme auf die kombinierten Hardware abbilden. Durch die Überlagerung und abschließendes Postprocessing wird der Raum abbildbarer Probleme allerdings noch deutlich erweitert. Nicht immer ist die Möglichkeit der Abbildung eines einzelnen Problems ohne weiteres zu erkennen. Mit Hilfe von neutralen Elementen wie 0 bei Addition/Subtraktion oder 1 bei Multiplikationen lassen sich beispielsweise Operationen "abschalten", ohne dass diese Möglichkeit explizit synthetisiert wurde. Auch die Assoziativität von Operationen kann die Abbildbarkeit eines Datenflussgraphen beeinflussen.

Student*in: Ramon Wirsch

Betreuer*in: Alexander Schwarz

Zeitraum: 24.04.2017 - 23.10.2017

Derzeit wird am Fachgebiet Rechnersysteme an AMIDAR-Prozessoren geforscht, die aus mehreren unabhängigen Funktionseinheiten aufgebaut sind und verschiedene Möglichkeiten der Rekonfiguration bereitstellen. Bisher lag der Fokus auf Ausführung von Java Bytecode, jedoch eignet sich das Grundprinzip für verschiedenste Instruktionssätze.

Es besteht die Idee, einen speziell auf das AMIDAR-Konzept zugeschnittenen Instruktionssatz zu entwickeln, der einige Gedanken von Datenflussarchitekturen aufgreift. Grundlegende Merkmale dieses neuen Instruktionssatzes sind bereits erarbeitet worden.

Aufgabe ist es, einen Simulator zu entwickeln, der Programme bestehend aus diesen Instruktionen ausführen kann. Mit Hilfe des Simulators soll die Anwendbarkeit des Instruktionssatzes verifiziert werden. Hierbei kann auf einen Assembler zurück gegriffen werden, um Programme zu erzeugen.

Student*in: Sebastian Herber

Betreuer*in: Kris Heid

Zeitraum: 01.08.2016 - 01.02.2017

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Der kritische Punkt, um die Leistungsfähigkeit von Manycore SoC Systemen zu steigern, ist momentan die Software. Durch die klassische iterative Denkweise beim Programmieren ist es relativ schwer die Software sinnvoll auf mehrere Rechenkerne aufzuteilen. In einer laufenden Arbeit wird versucht dieses Problem über Annotationen der Programmierer im Sourcecode zu umgehen und einzelne Aufgabenblöcke auf verschiedene Kerne aufzuteilen. Hierbei ist die Verwendung von globalen Variablen besonders kritisch. Allerdings müssten hierfür die Variablen zwischen allen Kernen synchronisiert werden. Dies wirft u.A. das Problem auf, was passiert, wenn bspw. eine globale Variable von zwei Kernen gleichzeitig beschrieben werden soll. Um ein aufwändiges Konfliktmanagement und die Synchronisation zu umgehen, soll ein Memory Kern existieren, von welchem alle anderen Kerne ihre globalen Variablen beziehen und welche nur dort geschrieben werden dürfen.

Ziel der Arbeit ist daher in dem Source to Source Compiler

Cetus einen Tranformation-Pass zu integrieren, welcher die Nutzung globaler Variablen in den einzelnen vom Nutzer definierten Task-Abschnitten erkennt. Anschließend müssen die globalen Variablen durch getter und setter Funktionen ersetzt werden.

Die reale Implementierung des hinter den getter und setter liegenden Speichers soll

in Form einer spezialisierten Peripherie-Komponente in die einzelnen Kerne eingeblendet werden. Anschließend soll eine abstrakte SoC Konfiguration ausgegeben werden, welche später zu einem lauffähigen System transformiert werden soll.

Projektseminare Bachelor

Student*in: Sebastian Focke und David Winter

Betreuer*in: Tajas Ruschke

Zeitraum: 01.06.2016 - 08.09.2017