EES²

Energy Efficient Simulation of Energy Efficient Storage for Neuromorphic Computing

Modern data centers consume gigantic amounts of energy. Developments around neuromorphic computing - computer architectures inspired by neuro-biological networks - have the potential to dramatically reduce this energy demand.

As part of the joint Sustainability Hub with Merck the project EES² of the departments Material Science and Electrical Engineering & Information Technology aims to develop simulation tools to predict material properties in energy-saving neuromorphic computer architectures. The result is a combination of research-scale model device components with compact modeling using hardware accelerated simulators for large circuits to enable researchers to determine which combination of memristor material and circuit type will operate with the highest efficiency for realistically sized computing architectures. Successful simulation helps to significantly shorten chip development cycles.

Motivation

Memristors as postulated by Leon Chua in the 1970s, are considered to be the fourth basic circuit element and essentially behave like resistors with a value that is depending on the current that flowed through it in the past. This allows them to store arbitrary values, both digital and analog and makes memristors a key element for energy efficient realizations of analog neuromorphic computing. Likewise this makes them a prime candidate for novel memory technologies. Different materials and principles can be used to build memristors, but the resulting properties and usability for various circuit structures are not easy to determine. To complicate matters, each application domain has vastly different requirements regarding e.g. the speed of reading/writing values, the required area or the precision and long term stability:

To fully evaluate the usability of a given memristor and its energy efficiency in a circuit, it is not enough to look at a single device in isolation, but rather full sized circuits have to be evaluated. This requires large amounts of processing time and large amounts of energy. Establishing an energy efficient chain from research-scale model devices to a realistic prognosis of what combination of material and circuit type will operate most energy efficiently is the goal of this project.

Overview

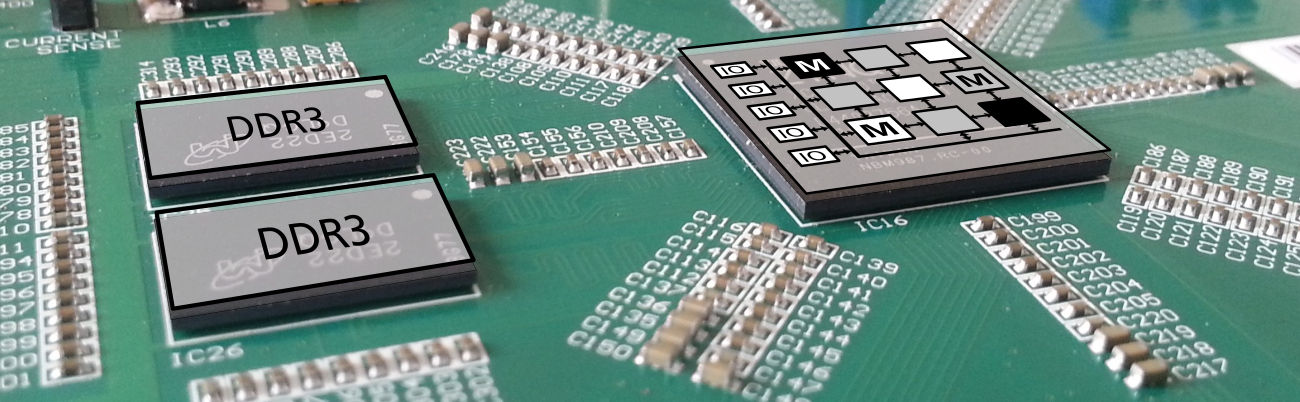

The simulation of memristors in the circuit simulation software SPICE requires multiple steps as shown below. This process starts with a SPICE model, which is a mathematical description of the physical device. Using this mathematical representation, all devices in the circuit are linearized based on a currently selected operating point. Using the linearization and all remaining circuit components, a equation system matrix is constructed and solved. If there is a valid solution, the operating point can be accepted and the simulation moves on to the next timestep, otherwise a new operating point has to be chosen and the circle repeats.

Since both linearization and solving the circuit equation system need to be done multiple times for each timestep of the simulation, this quickly adds up to millions of iterations for larger circuits. Implementing the linearization and other parts of the simulation into a specialized FPGA based hardware accelerator allows to greatly reduce runtime and energy needs of the simulation.

Research Plan

This project is split into three phases, each allocated with one year.

Phase 1: Foundation of Memristor Models and Accelerated Simulation

The first phase focuses on implementing a working path from device characterizations to hardware based computation of linearizations. This means searching for more precise memristor models and manually implementing them into SPICE and into a FPGA based hardware accelerator. These models will be calibrated with single devices to match real device behavior as closely as possible.

Goal: Hardware assisted analog simulation of 100s of memristor devices.

Phase 2: Refinement of Memristor Models and Simulator

The second phase focuses on further optimization of models and the simulator. This means calibration of models with small-scale array structures and incorporating device to device variability on the one hand and extending the hardware accelerated simulation to solve the linear equation system with hardware acceleration on the other hand.

Goal: Hardware based analog simulation of 1000s of memristor devices.

Phase 3: Generalization of Memristor Models and Automation of Simulator Adaptation

The final phase aims to develop a generic memristive model, which can be used to simulate different material systems. In this phase the HW based linearization will be generated by a software tool based on the model descriptions, first to code and then to hardware using a tool such as PIRANHA.

Goal: Easy adaptation of simulator to new memristor types and analog simulation of millions of devices.

Researchers

| Prof. Dr. Lambert Alff joined the Materials Science department of TU Darmstadt in 2005. Before he had the chair of Materials Science for Electrical Engineers in the EE department at TU Wien. His research focuses on advanced thin film technology for novel electronic devices. | Prof. Dr.-Ing. Christian Hochberger joined the EE department of TU Darmstadt in 2012. Before he was professor for embedded systems at TU Dresden since 2003. His research focuses on configurable technology and their uses in computer architecture. | Dr. Enrique Miranda is a Professor at the Department of Electronics Engineering, Universitat Autonoma de Barcelona, Spain since 2006. He is a Distinguished Lecturer from IEEE-Electron Devices Society since 2004 and his research interests are oxide reliability and memristive devices for neuromorphic computing. |

| Dr. Alexey Arzumanov joined the Material Science department's ATFT group of TU Darmstadt in 2017. He is focused on micropatterning, electrical and cryo measurements as well as experiment automation. | M.Sc. Jonas Gehrunger joined the Computer Systems Group in 2021 after finishing his master degree at TU Darmstadt. He is focused on efficient SPICE simulation of memristors. | Dr. F. Aguirre joined the Electronics Department of the Autonomous University of Barcelona (UAB) in 2022 after receiving his Ph.D. from the UTN-FRBA (Argentina) and keeping a very close and fruitful collaboration with the UAB since 2019. His research focuses on memristor modelling and memristive neuromorphic computing. |

| M.Sc. Eszter Piros is currently pursuing her Ph.D. at the Materials Science department of TU Darmstadt. Her research interests include oxide-based memristors as the building blocks of novel electronics and the occurring electronic fluctuations in these systems. |