Bachelor Theses

Student: Nora Simon

Supervisor: Ramon Wirsch

Time period: 01/20/2022 - 05/18/2022

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt. Hierzu sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Bei einer dieser Architekturen handelt es sich um RISC-V. Hierfür existiert bereits ein Demo-System bestehend aus dem Taiga RISC-V Prozessor und einem CGRA, allerdings mangelt es dem Taiga Prozessor noch an nativer Unterstützung von Fließkommazahlen in Form des RV32IMF Befehlssatzes . Diese soll im Rahmen dieser Arbeit nachgerüstet werden, um entsprechende Benchmarks in Hardware/auf FPGAs ausführen zu können.

Entsprechend der bereits durchgeführten Analyse soll FloPoCo 5 als Grundlage für die Fließkommaoperatoren genutzt werden. Eine möglichst identische Implementierung mit gleichen Operationen und Latenzen für CGRA und Taiga hat große Vorteile für die Vergleichbarkeit, weshalb eine zukünftige Portierung der Fließkommaoperatoren für den CGRA berücksichtigt werden soll.

Student: Julian Veit

Supervisor: Ramon Wirsch

Time period: 04/11/2022 - 09/26/2022

Am Fachgebiet Rechnersysteme werden Hardwarebeschleuniger für eine Reihe von Architekturen entwickelt, unter anderem für RISC-V und IBM Z-Architekturen. Hierzu sollen reguläre Programme ohne jegliche Anpassungen an den Hardwarebeschleuniger zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können.

Um Code-Abschnitte als Kandidaten für Hardware-Beschleunigung zu identifizieren, wird üblicherweise nach Schleifen gesucht in denen ein erheblicher Anteil der Rechenzeit verbracht wird. Anschließend können diese, auch Hot-Spots genannten Schleifen, weiter auf Eignung für die Hardware-Beschleunigung untersucht werden.

Ziel dieser Arbeit ist es insbesondere einen Loop-Profiler für die RISC-V Architektur zu entwerfen. Dieser soll in den Taiga RISC-V Prozessor integriert werden, wo er zur Laufzeit Schleifen finden und Iterationen sowie Aufruf-Häufigkeit analysieren soll. Die so gewonnen Daten sollen vom Prozessor selbst abrufbar sein und die Grundlage bilden für die weitere Auswahl von Schleifen für die Beschleunigung mittels unseres Hardware-Beschleunigers.

Student: Nico Rieckhoff

Supervisor: Ramon Wirsch

Time period: 05/02/2022 - 09/05/2022

Am Fachgebiet Rechnersysteme werden eine Reihe von Architekturen mitteles Coarse-Grained Reconfigurable Arrays (CGRAs) beschleunigt. Hierbei sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Eines dieser Zielsysteme ist der RISC-V Prozessor Taiga, der für die Benutzung auf FPGAs entworfen wurde. Er wurde bereits Cache-Kohärent mit dem CGRA zu einem Demonstationssystem kombiniert. Und ist mit vorbereiteten CGRA-Kerneln laufwendig. Es existierenden auch bereits Code um das nachträgliche Überschreiben von Instruktionen im Speicher durchzuführen, das benötigt wird um zur Laufzeit entdeckte Kernel anzuwenden.

Da der Beschleunigungsprozess ("Synthese") letztendlich vollständig nebenläufig auf dem Taiga Prozessor laufen soll, möglichst nebenläufig und unabhängig vom jeweiligen Nutzerprogramm, wird eine mit allen Bestandteilen des Systems abgestimmte Softwareumgebung für die Ausführung auf dem Taiga Prozessor benötigt. Diese Umgebung muss, ähnlich zu Echtzeitbetriebsystemen die Rechenzeit des Systems auf die Beschleunigung und das eigentliche Nutzprogramm verteilen. Weiterhin muss dabei die Beschleunigung mit dem Nutzprogramm synchronisiert werden, weil dazu zur Laufzeit in das originale Programm, durch Umschreiben des Codes ("Patchen"), eingegriffen werden muss. Die Umgebung soll auch den CGRA, die vorhandenen Kernel und den noch in der Entwicklung befindlichen Loop-Profiler managen. Um das Beschleunigen von möglichst vielen und verschiedenen Nutzprogrammen möglichst einfach zu machen, soll vom Nutzer keine aufwendige Integration in das Nutzprogramm erforderlich sein. Im Idealfall kann diese Umgebung deshalb in den bereits vorhanden Bootloader integriert werden, so dass gar keine gesonderte Anpassung des Nutzerprogramms erforderlich ist.

Student: Jonas Schoenen

Supervisor: Tobias Schladt

Time period: 04/11/2022 - 09/12/2022

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Eine einzige defekte Speicherzelle mit undefiniertem Zustand führt dazu, dass klassische Look-up-Tables (LUTs) nur noch zur Hälfte nutzbar sind. Beim Entwurf von Logik-Elementen für NV-FPGAs müssen potentielle Fehler und ihre Auswirkungen also im Sinne einer besseren Fehlertoleranz berücksichtigt werden.

Ziel dieser Arbeit ist es, eine neue Architektur für die Logik-Elemente von NV-FPGAs zu entwerfen und diese auf ihre Fehlertoleranz hin zu evaluieren.

Student: Lukas Freiberger

Supervisor: Tobias Schladt

Time period: 11/15/2021 - 02/07/2022

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Diese potentiellen Fehler müssen bei der Logiksynthese für NV-FPGAs beachtet werden.

Ziel dieser Arbeit ist es, fehlerbehaftete Routing-Elemente in den Logiksynthese-Prozess des Tools "Versatile Place and Route" (VPR), das Teil der Toolchain "Verilog-to-Routing" (VTR) ist, zu integrieren. Anschließend soll die Auswirkung der Fehler auf das Routing evaluiert werden.

Master Theses

Student: Simon Vetter

Supervisor: Ramon Wirsch

Time period: 07/05/2021 - 01/03/2022

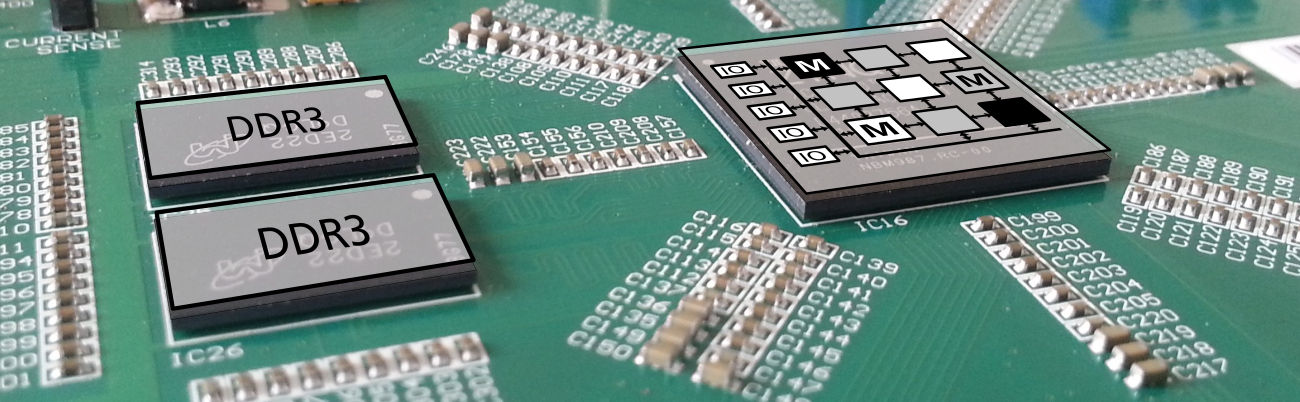

Am Fachgebiet Rechnersysteme werden eine Reihe von Architekturen mitteles Coarse-Grained Reconfigurable Arrays (CGRAs) beschleunigt. Hierbei sollen reguläre Programme zur Laufzeit analysiert und partiell mit dem Hardwarebeschleuniger ausgeführt werden können, ohne dass sie vorher dafür angepasst werden müssen.

Es existiert bereits ein Demonstator auf FPGA-Basis für das CGRA zusammen mit einem RISC-V Prozessor. Allerdings ist die Cache- und Speicher-Anbindung des CGRAs noch nicht ausgereift oder optimiert. Auch fehlt die Unterstützung von Prefetching von Speicherinhalten für das CGRA, so dass regelmäßig gestalled wird, weil sich Speicherinhalte noch nicht in den Caches befinden.

Ein Vorläufer des aktuellen CGRAs hatte bereits Prefetching-Support in Kombination mit dem AMIDAR-Prozessor. Durch den Wechsel der Host-Architektur hin zu RISC-V und einer grundlegenden Aktualisierung des CGRAs ist diese Funktionalität verloren gegangen und soll jetzt nachgerüstet werden.

Student: Lucas Gaia de Castro

Supervisor: Tobias Schladt

Time period: 03/30/2022 - 09/28/2022

In FPGAs werden zur Speicherung der Konfigurationsdaten SRAM-Speicherzellen verwendet. Diese stellen einen flüchtigen Speicher dar, verlieren also bei Unterbrechung der Spannungsversorgung ihre Information. Deswegen wird an Non-Volatile (NV)-FPGAs geforscht, die nicht-flüchtigen Konfigurationsspeicher besitzen. Eine Möglichkeit, diese zu implementieren, stellen Speicherzellen auf Memristor-Basis dar.

Memristoren sind passive Bauelemente, deren Widerstandswert von der Vorgeschichte des hindurchgeflossenen Stromes abhängt. Aufgrund der additiven Fertigung von Memristor-basierten Speichern ist davon auszugehen, dass ein gewisser Anteil der Speicherzellen fehlerbehaftet ist. Durch die mehrstufigen Pass-Transistor-Schaltungen, die in der Routing-Architektur von FPGAs eingesetzt werden, wirken sich Speicherzellenfehler auf große Teile des Routing-Netzes aus. Beim Entwurf einer Routing-Architketur für NV-FPGAs müssen potentielle Fehler und ihre Auswirkungen also berücksichtigt werden.

Ziel dieser Arbeit ist es, eine neue Architektur für die Routing-Elemente von NV-FPGAs zu entwerfen und diese auf ihre Fehlertoleranz hin zu evaluieren.

Student: Uzay Yavuz

Supervisor: Jonas Gehrunger

Time period: 11/15/2021 - 05/16/2022

Am Fachgebiet Rechnersysteme wird im Rahmen des (EES)²-Projektes die Hardware-Beschleunigung der Schaltungssimulation von Memristoren mithilfe der Software SPICE untersucht. Dabei werden Modelle der Schaltungselemente in einem Hardwarebeschleuniger parallelisiert ausgewertet. Da ein großer Teil der verbleibenden Simulationszeit auf die Lösung des linearen Gleichungssystems der Schaltung entfällt, soll dies ebenfalls in Hardware erfolgen.

Die Struktur der von SPICE erzeugten Schaltungsmatrizen ist sehr dünnbesetzt (sparse), wofür es spezialisierte Solver gibt. Einer davon ist das KLU Verfahren. Dieses soll für ein FPGA-System implementiert werden, wobei die Implementation parametrisierbar in Bezug auf Datentyp und zugewiesenen Ressourcen erfolgen soll.

Um eine einfache Skalier- und Parametrisierbarkeit zu ermöglichen, soll die Implementation dabei in der Hardware-Beschreibungssprache Chisel entwickelt werden.

Student: Jian Liu

Supervisor: Jonas Gehrunger

Time period: 12/09/2021 - 06/09/2022

Am Fachgebiet Rechnersysteme wird im Rahmen des (EES)²-Projektes die hardwarebeschleunigte Schaltungssimulation von Memristoren mithilfe der Software SPICE untersucht. Dabei werden Modelle der Schaltungselemente in einem Hardwarebeschleuniger parallelisiert ausgewertet und das entstandene Gleichungssystem gelöst. Ein Weg, die Effizenz der Simulation weiter zu erhöhen, besteht in der Verwendung von Zahlendarstellungen und Berechnungen mit reduzierter Genauigkeit.

Um die Auswirkung von Änderungen an der Genauigkeit abzuschätzen, soll die Open-Source Software ngspice um eine Instrumentierung erweitert werden, die eine einstellbare Veränderung der Genauigkeit von Berechnungen erlaubt. Dafür sollen zunächst während laufender Simulationen der auftretende Dynamikbereich überwacht werden.

Anschließend sollen innerhalb der Berechnungen Werte mit minimalem und maximalem Betrag erzwungen sowie eine Quantisierung durchgeführt werden, um reduzierte Genauigkeit zu simulieren. Mit diesen Änderungen soll das Verhalten der Simulation analysiert werden, etwa in Bezug auf den Spannungsverlauf und das Konvergenzverhalten.

Project Seminars Master

Student: Philipp Müller

Supervisor: Ramon Wirsch

Time period: 10/01/2021 - 02/20/2022

Am Fachgebiet Rechnersysteme werden mehrere taktgenaue Simulatoren verwendet. Die neuesten 3 davon, basieren auf der gemeinsamen Grundlage des Simulator Frameworks.

Die Simulatoren werden für Benchmarks und Tests verwendet und sollen in Zukunft auch in studentischen Praktika für Aufgaben genutzt werden. Hierzu sollen sie möglichst schnell laufen.

Im Rahmen dieses Projektseminars sollen insbesondere zwei Methoden zur Beschleunigung des Frameworks erprobt werden. Beide sind dabei unabhängig von der simulierten Zielarchitektur zu nutzen, so dass sie möglichst für alle Simulatoren Vorteile bringen.

Es soll sowohl die Byte Code Generierung zur Laufzeit für simple, aber besonders Performance kritische stellen erprobt werden, also auch die automatische Source Code Generierung. Beide Verfahren erlauben so dem Framework eine automatische Anpassung auf die Zielsimulation, für eine Beschleunigung. Beide Verfahren sind ausführlich zu evaluieren. Die Ergebnisse könnten in anderen Arbeiten als Grundlage für die weitere, simulations-spezifische Beschleunigung genutzt werden.