Bachelor Theses

Student: Florian Prott

Supervisor: Boris Dreyer

Time period: 05/01/2015 - 06/12/2016

Für die Korrektheit von sicherheitskritischen eingebetteten Systemen ist es nicht nur wichtig, dass Programme korrekte Ergebnisse berechnen, sondern dass sie diese auch rechtzeitig liefern. Um dies sicherzustellen, muss die Worst Case Execution Time (WCET) des Programms bestimmt werden. Die WCET eines Programms setzt sich aus der WCET von einzelnen Basic Blocks (BB) zusammen. Ein BB ist eine nicht verzweigende Sequenz von Instruktionen. Ein Programm besteht daher aus hunderttausenden von BBs, die aus nur wenigen Instruktionen bestehen können.

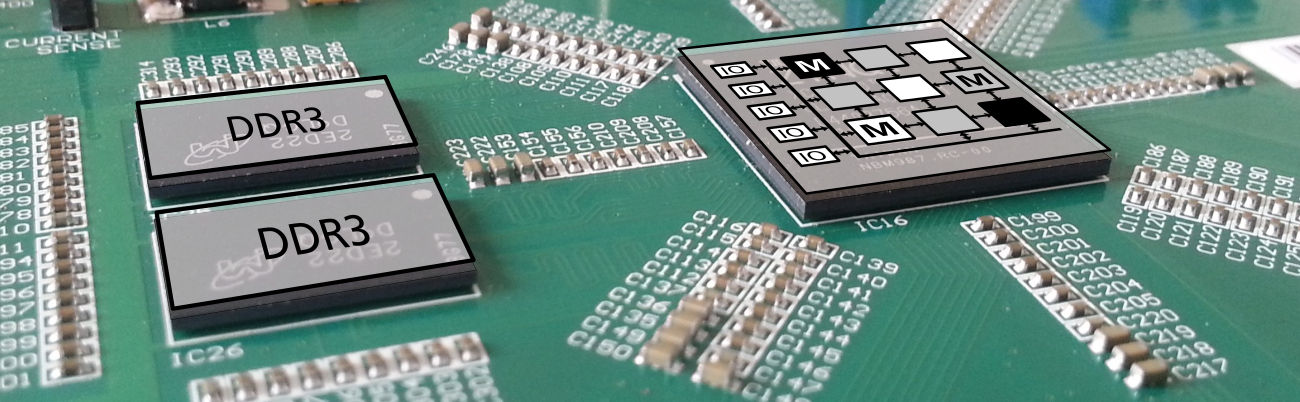

Für jeden BB wird eine Statistik über dessen Ausführungszeit erstellt. Aufgrund der großen Anzahl an BBs und den Timing-Anforderungen, sollen diese Statistiken in Reduced Latency DDR (RLDRAM) geführt werden.

Ziel dieser Arbeit ist das Design und die Implementierung eines RLDRAM-Controllers zur dynamischen Programmanalyse. Diese Hardwarekomponente soll auf einem bestehenden RLDRAM-Controller aufsetzen und diesen um vier unabhängige Lese- und Schreibports erweitern. Anschließend soll einer dieser Ports an den SpartanMC angebunden werden, um auf den Speicher auch per Software Zugriff zu erlangen.

Student: Hu Yue

Supervisor: Boris Dreyer

Time period: 10/20/2015 - 01/20/2016

Für die Korrektheit von sicherheitskritischen eingebetteten Systemen ist es nicht nur wichtig, dass Programme korrekte Ergebnisse berechnen, sondern dass sie diese auch rechtzeitig liefern. Um dies sicherzustellen, muss die Worst Case Execution Time (WCET) des Programms bestimmt werden. Die WCET eines Programms setzt sich aus der WCET von einzelnen Basic Blocks (BB) zusammen. Ein BB ist eine nicht verzweigende Sequenz von Instruktionen. Ein Programm besteht daher aus hunderttausenden von BBs, die aus nur wenigen Instruktionen bestehen können.

Mittels dynamischer Programmanalyse kann die WCET und weitere Zeiten eines Programms gemessen werden. Hierbei wird die Ausführungszeit eines jeden einzelnen BBs gemessen und eine Statistik geführt. Ein Modul, welches diese Messungen durchführt ist bereits vorhanden.

Ziel dieser Arbeit ist der Entwurf und die Implementierung eines Statistik-Moduls, das die WCET, Average Case Execution Time (ACET) und die Best Case Execution Time (BCET) eines jeden BBs bestimmt. Wird dem Modul signalisiert, dass laufende Programmanalyse beendet ist, so soll die Statistik per USB auf auf einen Host-Computer übertragen werden. Die Übertragung soll auf Basis des SpartanMC geschehen, welcher USB-Kommunikation unterstützt.

Student: Steffen Grimm

Supervisor: Philip Gottschling

Time period: 11/01/2015 - 04/30/2016

Um einen für eine bestimmte Aufgabe spezialisierten Datenpfad zu erstellen wird ein vorliegender Datenflussgraph in Hardware umgesetzt. Der Datenpfad erfüllt dann genau die vom Nutzer gewünschte Funktion. Um eine andere Funktion zu realisieren wird eine neuer Datenpfad erstellt. Das Erstellen des Datenpfades (Syntheseprozess) benötigt allerdings viel Zeit. Effizienter ist es daher, einen Datenpfad zu erstellen, der bereits mehrere Funktionen realisieren kann und nur noch konfiguriert werden muss.

Diese Arbeit befasst sich mit der Überlagerung von Datenflussgraphen bzw. mit der Erweiterung eines bestehenden Datenpfades. Damit würden zunächst zwei oder mehrere Datenflussgraphen überlagert und erst danach ein Datenpfad erstellt, der dadurch mindestens alle gewünschten Funktionen bereitstellt. Dazu müssen Kommpatibilitätsgraphen (zwischen Datenflussgraph und bestehendem Datenpfad) erstellt und danach die größtmögliche Kompatibilität gefunden werden.

Student: Karsten Müller

Supervisor: Lukas Jung

Time period: 11/02/2015 - 04/04/2016

Student: Patrick Appenheimer

Supervisor: Lukas Jung

Time period: 06/27/2016 - 11/26/2016

Coarse Grained Reconfigurable Arrays (CGRAs) werden in AMIDAR-Prozessoren als Hardware Beschleuniger verwendet. Eine hohe Beschleunigung wird dabei erreicht, wenn das CGRA über mehrere DMA-Schnittstellen verfügt, über welche auf den Speicher zugegriffen werden kann. Dabei verfügt jede Schnittstelle über einen eigenen Cache.

Im Zuge dieser Arbeit soll ein Verfahren entwickelt werden, welches Cache-Kohärenz sicherstellt. Dies kann zum einen mit Hilfe von bekannten Kohärenz-Protokollen erreicht werden. Darüber hinaus muss untersucht werden, ob durch geeignete Programmierung des CGRAs sichergestellt werden kann, dass Inkonsistenzen in den Caches gar nicht oder nur selten auftreten.

Student: Hendrik Schöffmann

Supervisor: Lukas Jung

Time period: 01/01/2016 - 04/01/2016

Die Hardware Synthese ist ein wichtiges Werkzeug in AMIDAR zur automatischen Generierung von Hardware Beschleunigern zur Laufzeit. Der Synthese-Algorithmus kann dabei über Zahlreiche Parameter an die aktuelle Anwendung angepasst werden. Zur Zeit werden empirisch gefundene Werte verwendet, welche im Mittel zu guten Ergebnissen führen.

Im Zuge dieser Arbeit soll ein Verfahren entwickelt werden, welches es erlaubt mit Hilfe von Mustererkennung die optimalen Parameterwerte für eine gegebene Anwendung zu finden.

Da der Synthese-Algorithmus permanent weiterentwickelt wird, soll das Verfahren leicht anpassbar und wiederholbar sein.

Student: Marek Völker

Supervisor: Changgong Li

Time period: 12/01/2015 - 05/01/2016

Bisherige Arbeiten (www.amidar.de) haben gezeigt das ein deutliches Beschleunigungspotential für Applikationen im Bereich der eingebetteten Systeme besteht.

Ziel dieser Arbeit soll es sein, den Heap eines AMIDAR basierten Java-Prozessor um einen Garbage Collector zu erweitern. Dieser soll auf einem FPGA in Verilog implementiert werden. Der dadurch entstehende Garbage Collector soll parallel mit dem Prozessor laufen können, ohne (oder möglichst selten) die fließende Ausführung einer Anwendung unterbrechen zu müssen.

Teilaufgaben:

- Garbage Collection Algorithmus auf Basis des vorhandenen Prozessormodells entwerfen

- Schnittstellen zu den betroffenen Funktionseinheiten definieren

- Algorithmus implementieren und testen

Student: Jakob Karg

Supervisor: Changgong Li

Time period: 03/01/2016 - 08/01/2016

Bisherige Arbeiten (www.amidar.de) haben gezeigt das ein deutliches Beschleunigungspotential für Applikationen im Bereich der eingebetteten Systeme besteht.

Im Rahmen dieser Arbeit sollen die beiden vorhandenen ALUs wie folgt optimiert werden:

- Implementierung eines Newton-Raphson-Dividierers für die beiden ALUs

- Beschleunigung der IALU durch neue Implementierung der vorhandenen Pipeline

- Erweiterung der FALU um eine Pipeline

Student: Melanie Braun

Supervisor: Kris Heid

Time period: 02/22/2016 - 07/22/2016

Das bisherige SpartanMC-SoC-Kit ermöglicht bereits das komfortable Zusammenstellen eines SoC nach eigenen Wünschen über eine grafische Oberfläche. Jedoch muss der Nutzer Aus-/Eingänge der hinzugefügten Komponenten manuell verknüpfen und konfigurieren, was eine sehr zeitraubende und fehleranfällige Arbeit ist.

Durch diese Arbeit soll der Schritt der manuellen Konfiguration nahezu hinfällig werden. Hierzu sollen alle Komponenten mit Intelligenz in Form von ausführbaren LUA-Skripten in deren Modulbeschreibung ausgestattet werden. Durch diesen Schritt könnten sich die Komponenten beim Hinzufügen selbst konfigurieren und beispielsweise bereits eindeutig zusammengehörige Ein-/Ausgänge miteinander verknüpfen. Hierdurch würde diese Arbeit die SoC Konfiguration innerhalb von einem Bruchteil der bisherigen Zeit ermöglichen und außerdem die Komplexitätshürde erheblich senken.

Student: Joris Beringer

Supervisor: Kris Heid

Time period: 10/01/2015 - 03/01/2016

Um die Funktionalität des Prozessors nach solchen Erweiterungen zu sichern, ist eine gute Testumgebung für Regressionstests unerlässlich. Deshalb soll im Rahmen der Arbeit eine Testumgebung implementiert werden, die es ermöglicht, sowohl den kompletten Befehlssatz als auch relevante Kombinationen von Befehlen zu testen. Dazu soll ein Testfallgenerator entwickelt werden, mit dem es möglich ist, entsprechenden Testcode zur Verhaltenssimulation, zum Test des Prozessor in realer Hardware und für den SpartanMC Simulator zu erstellen. Dabei muss es möglich sein ohne hohen Aufwand das Testszenario um zusäzliche Tests, zum Beispiel für neue Befehle, zu erweitern.

Student: Laurenz Kamp

Supervisor: Kris Heid

Time period: 08/01/2016 - 11/01/2016

Student: Felix Sterzelmaier

Supervisor: Kris Heid

Time period: 10/19/2015 - 03/21/2016

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Es besteht bereits die Möglichkeit mehrere SpartanMC Kerne auf einem FPGA unter zu bringen und diese über einfache send und receive Funktionen kommunizieren zu lassen. Eine solche Kommunikation ist momentan allerdings nur möglich, wenn zwischen beiden Kernen eine direkte Verbindung besteht. Ziel der Arbeit ist die Unterstützung von Nachrichtenrouting. Mit Hilfe von Routing sollen alle Kerne unabhängig von der zugrunde liegenden Vernetzung miteinander Kommunizieren können.

In einer vorangegangenen Arbeit wurde bereits mit der Implementierung eines circuit switching Routers begonnen, welcher weiterentwickelt werden soll.

Student: Mohammadmehdi Peiro

Supervisor: Kris Heid

Time period: 07/01/2016 - 12/01/2016

Am Fachgebiet Rechnersysteme wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Ein Hauptaugenmerk bei der Weiterentwicklung des SpartanMC Toolkits liegt aktuell auf der Erweiterung der Multi-Core Fähigkeit des SpartanMC. Um die erstellten Multi-Core Systeme zu testen, fehlt allerdings momentan noch eine gewisse Bandbreite an guten Anwedungen. Die Parsec Benchmark Suite beherbergt eine Reihe von Anwendungen, die speziell auf Multithreading ausgelegt sind.

Ziel dieser Arbeit soll daher die Portierung von Parsec Benchmarks auf SpartanMC sein. Viele Anwendungen sind bereits als C-Sourcecode in Parsec enthalten und müssen nur auf die vergleichsweise eingeschränkte SpartanMC Plattform angepasst werden. So hat der SpartanMC beispielsweise kein Dateisystem aus dem Eingabedaten gelesen werden können. Die Eingabedaten müssen dann entweder komplett als Array in Datenspeicher abgelegt werden oder per USB zur Laufzeit übertragen werden.

Idealerweise sollte während der Arbeit noch die Parallelisierbarkeit der Anwendungen, mit Hilfe des von uns entwickelten parallelisierenden Compilers, getestet und evaluiert werden

Student: Nourhan El-Hamawy

Supervisor: Kris Heid

Time period: 03/29/2016 - 08/30/2016

Zur Programmierung des SpartanMC wird die GNU Toolchain verwendet. Darin werden die Binutils für das Handling von Objekt-Dateien und Binärprogrammen verwendet. Leider unterstützt die aktuelle Portierung der Binutils nicht die Verarbeitung von Debug-Informationen.

Durch eine frühere Arbeit wurden bereits weitestgehend DWARF konforme Debug Daten während der Kompilierung erzeugt. In dieser Arbeit sollen diese Daten nun ausgewertet und die Informationen als Sourcecode-Annotationen in den SpartanMC Simulator eingetragen werden. Dieser Schritt ermöglicht das Debugging von Programmen nicht nur auf Assembler- sondern auch wesentlich komfortabler auf C-Ebene.

Master Theses

Student: Hengxin Zhou

Supervisor: Tajas Ruschke

Time period: 05/16/2016 - 11/15/2016

Student: Lukas Jäger

Supervisor: Dennis Wolf

Time period: 04/07/2016 - 10/07/2016

Coarse Grained Reconfigurable Arrays (CGRA) sind Schaltungen, die zumeist als Hardwarebeschleuniger eingesetzt werden. Einzelne Rechenzellen verarbeiten entsprechend eines im voraus definierten Operationsplans (Scheduling) Daten massiv parallel. Das Operationssprektrum der einzelnen Rechenzellen sowie die Verbindung untereinander sind generisch und im Einzelfall entscheidend für die Laufzeit einzelner Applikationen.

In dem Projekt "UltraSynth" soll entsprechend mehrerer Beispielapplikationen ein CGRA für die entsprechende Anwendungsdomäne automatisiert erstellt und implementiert werden. Die Erzeugung einer optimalen CGRA Komposition (bzgl. Anzahl an Rechenzellen und deren Operationsspektrum) ist dabei aufgrund der Komplexität nicht mehr möglich. In solchen Fällen werden Heuristiken genutzt, die darauf setzen ein nicht optimales aber ausreichend gutes Ergebnis zu liefern. Für das vorliegende Optimierungsproblem kann eine Heuristik der evolutionären Algorithmen (EA) genutzt werden. Dazu ist eine Schätzung der benötigten Resourcen und des maximalen Taktes auf einem FPGA notwendig, da diese weitere Kostenfunktionen eines EA darstellen - neben der Laufzeit eines Programmes auf der Komposition. Dies soll außerdem sicher stellen, dass unnötige Synthese- und Implementierungsvoränge minimiert oder gar vermieden werden können.

Diese Arbeit ist in mehrere Schritte unterteilt. Zuerst soll aufbauend auf exemplarischen Implementierungen ein Schätzer des Resourcenverbrauchs und der maximalen Taktfrequenz realisiert werden. Mit Hilfe der insgesamt 3 Kostenfunktionen soll dann ein passender evolutionärer Algorithmus umgesetzt werden. Im besten Fall soll zuletzt eine Senkung der Laufzeit erreicht werden, indem anhand der gegebenen Applikationen Parameter der Heuristik automatisch kalibriert werden.

Student: Thomas Ballenthin

Supervisor: Boris Dreyer

Time period: 10/15/2015 - 03/15/2016

Für die Korrektheit von sicherheitskritischen eingebetteten Systemen ist es nicht nur wichtig, dass Programme korrekte Ergebnisse berechnen, sondern dass sie diese auch rechtzeitig liefern. Um dies sicherzustellen, muss die Worst Case Execution Time (WCET) des Programms bestimmt werden. Die WCET eines Programms setzt sich aus der WCET von einzelnen Basic Blocks (BB) zusammen. Ein BB ist eine nicht verzweigende Sequenz von Instruktionen. Ein Programm besteht daher aus hunderttausenden von BBs, die aus nur wenigen Instruktionen bestehen können.

Mittels dynamischer Programmanalyse kann die WCET und weitere Zeiten eines Programms gemessen werden. Hierbei wird die Ausführungszeit eines jeden einzelnen BBs gemessen und eine Statistik geführt. Ein Modul, welches diese Messungen durchführt ist bereits vorhanden.

Ziel dieser Arbeit ist der Entwurf und die Implementierung eines Statistik-Moduls, basierend auf einem Histogramm. Hierzu erhält das Modul die gemessenen Ausführungszeiten der BBs und aktualisiert daraufhin entsprechend das Histogramm.

Student: Philipp Käsgen

Supervisor: Philip Gottschling

Time period: 04/01/2016 - 09/30/2016

Im Bereich der High-Level-Synthese wird oft ein bestehender Daten- und Kontrollflussgraph in einen Datenpfad übersetzt. Die anschließende Hardware-Synthese für ein FPGA kann dabei je nach Problemgröße bis zu einigen Stunden dauern. Ändert man die Funktion oder nur einen Wert innerhalb des Datenflussgraphen, muss die Synthese erneut durchgeführt werden. Bei sich häufig ändernden Funktionen, ist dieses Vorgehen so nicht praktikabel. Wesentlich effizienter ist es daher, aus der Superposition mehrerer Ausgangs-Datenflussgraphen einen überlagerten Datenflussgraph zu erstellen, der je nach Konfiguration alle gewünschten Funktionalitäten implementiert. Zur Superposition werden Kompatibilitätsgraphen erzeugt, aus denen sich mit Hilfe von maximalen Cliquen der größte gemeinsame Teil zweier Datenflussgraphen ermitteln lässt.

Das Cliquenproblem ist schon lange bekannt und Gegenstand vieler Forschungsarbeiten aus dem Bereich der Mathematik. Derzeit wird das Problem mit Hilfe eines Algorithmus von Bron und Kerbosch gelöst, der allerdings eine exponentielle Komplexität aufweist. Zwar existieren Heuristiken, die das Problem in polynomieller Zeit lösen, diese können allerdings die Struktur von Kompatibilitätsgraphen nicht ausnutzen. Ziel dieser Arbeit ist es daher, ein Verfahren zu entwickeln und zu implementieren, dass die größte maximale Clique in einem automatisch generierten Kompatibilitätsgraphen findet.

Student: Marcel Jourdan

Supervisor: Changgong Li

Time period: 03/01/2016 - 09/01/2016

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. In diesem Modell werden Instruktionen in eine Komposition von so genannten Tokens zerlegt, die dann an einzelne Funktionseinheiten verteilt werden. Die Funktionseinheiten koordinieren ihre Arbeit über die Daten, die sie produzieren oder konsumieren.

Der aktuelle Object-Heap des Prozessors erlaubt nur den Anschluss einfacher, kleiner Peripheriekomponente mit separaten Registern (z.B. UART). So eine Peripherie lässt sich dann in einer Java-Anwendung als normales Objekt deklarieren und verwalten, wobei deren Register auf primitive Datenfelder des Objektes abgebildet werden können. Aber ein kompliziertes Gerät wie der Ethernet-Controller besitzt typischerweise große Datenstrukturen (z.B. FIFO), die nicht mehr als primitives Feld umsetzbar sind. Idealerweise sollen solche Datenstrukturen als Java-Array definiert und genutzt werden, um die nahtlose Verbindung externer Geräte mit dem AMIDAR-Prozessor auf der Java-Ebene grundsätzlich zu ermöglichen.

Ziel dieser Arbeit soll es sein, das bisherige Peripheriemodell von AMIDAR um den DMA-Anschluss zu erweitern. Über diesen Anschluss soll der Austausch großer Datenmengen zwischen einer Peripherie und dem Heap schnell und transparent stattfinden können. Auf Basis des erweiterten Modells soll exemplarisch ein DMA-fähiger Ethernet-Controller sowie ein praxisnaher Benchmark realisiert werden.

Student: Jan Andresen

Supervisor: Changgong Li

Time period: 11/01/2015 - 05/01/2016

Bisherige Arbeiten (www.amidar.de) haben gezeigt, dass ein deutliches Beschleunigungspotential für Applikationen im Bereich der eingebetteten Systeme besteht.

Das aktuelle Bus-Protokoll erlaubt nur M:1 Verbindung. Das heißt dass mehrere Busse am Eingang einer einzelnen Funktionseinheit angeschlossen werden dürfen, aber deren Ausgang nur an einem dieser Busse. Die Ausbauflexibilität und Performanz des ganzen Systems wird dadurch eingeschränkt. Im Rahmen dieser Arbeit soll das Bus-Protokoll erweitert werden, um M:N Verbindung zu unterstützen. Außerdem muss das erweiterte Bus-Protokoll zusätzliche Schnittstellen besitzen damit ein CGRA nahtlos mit AMIDAR-Prozessoren verbunden werden kann.

Student: Syed Abdul Majid Ali

Supervisor: Dennis Wolf

Time period: 04/01/2016 - 09/30/2016

Am Fachgebiet Rechnersysteme wurde das Modell eines adaptiven Prozessors entwickelt (AMIDAR). Dieses Modell erlaubt es zur Laufzeit auf spezifische Anforderungen einer Applikation zu reagieren. Dazu zählt die Erkennung von rechenintensiven und wiederkehrenden Schleifen und deren Abbildung auf einem Coarse Grained Reconfigruable Array (CGRA). CGRAs sind Arrays aus Rechenzellen, die Instruktionssequenzen massiv parallel verarbeiten können. 2015 wurde hierfür eine generische CGRA Architektur implementiert. Mittels eines Generators können beliebige CGRA Instanzen in Verilog erzeugt werden, ohne dabei den Verilog Code manuell anpassen zu müssen. Die Architektur beherrscht zum jetzigen Zeitpunkt Arithmetik und Kontrollflussoperationen auf Basis von Festkommadarstellung. Um ohne Einschränkung Kernels abbilden zu können, ist es allerdings notwendig auch Gleitkommaberechnungen durchführen zu können.

Daher soll im Rahmen dieser Arbeit das CGRA um Gleitkommaoperationen und Datentypkonvertierungen erweitert werden. Dabei gilt es im ersten Schritt auch eine strategisch sinnvolle Auswahl an Implementierungen zu treffen. Neben der generischen Implementierung soll sich die Arbeit auf ausführlichen Tests und die Verifikation durch Eigenschaftsnachweise (Property Checking) konzentrieren.

Student: Alexander Weisel

Supervisor: Changgong Li

Time period: 04/25/2016 - 10/25/2016

Am Fachgebiet Rechnersysteme wird momentan ein

Ziel dieser Arbeit ist die Implementierung von

Im nächsten Schritt soll das vollständige

Auf Basis der obigen zwei Schritte soll RMI zunächst für ein einfaches Client-Server-System realisiert werden, welches aus einem AMIDAR-System (Client) und einem PC (Server) besteht. Dabei soll eine vollständige AXT-Datei auf der AMIDAR Seite vorher geladen werden. Mithilfe von RMI soll der Client in der Lage sein, Methoden auf dem Server auszuführen.

Student: Alexander Schwarz

Supervisor: Changgong Li

Time period: 10/01/2015 - 03/31/2016

FPGAs sind in den letzten Jahren kontinuierlich günstiger geworden und haben mittlerweile ein Preisniveau erreicht, welches es erlaubt, diese Bausteine ganz regulär für die Implementierung von System-on-Chip (SoC) zu verwenden. Aber aufgrund ständig steigender Größe und Komplexität von SoCs sind diese immer schwieriger zu debuggen und zu testen. Damit das Debugging eines komplexen, FPGA basierten Systems leichter vorgenommen werden kann, stellen die meisten FPGA-Hersteller spezielle Interfaces bereit, welche das Auslesen eines kompletten Designs aus einem FPGA als Bitstream in Echtzeit erlauben.

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells (www.amidar.de) implementiert, welches es dem Prozessor erlaubt, zur Laufzeit einer Applikation auf deren spezifische Anforderungen zu reagieren. Im Laufe des Projekts wird das Debugging des Prozessors durch Hinzufügen unterschiedlicher Funktionseinheiten immer komplizierter, wobei eine Post-Synthesis-Simulation schon nicht mehr ausreicht.

Ziel dieser Arbeit ist die Entwicklung einer Debug Perspektive in Eclipse, welche ein Bitstream von einem Xilinx-FPGA analysieren und anschießend die aktuellen Zustände einzelner Funktionseinheiten textuell oder graphisch darstellen kann. Hierfür soll auch ein Break-Point Mechanismus entworfen werden, welcher ermöglicht, ein SoC an einer bestimmten Programmstelle anzuhalten und dann das ganze Design über einen JTAG-Port auszulesen.

Wünschenswert ist außerdem, dass das entstehende Tool auch auf andere SoC Architekturen übertragen werden kann (z.B. SpartanMC).

Student: Taimoor Naveed

Supervisor: Tajas Ruschke

Time period: 04/04/2016 - 10/04/2016

Am Fachgebiet Rechnersysteme wird momentan ein Java-Prozessor auf Basis des AMIDAR-Modells implementiert, dem ein CGRA (coarse grained reconfigurable array) für die dynamische Beschleunigung des Programmablaufs zur Verfügung steht.

Damit ein Programmteil auf das CGRA abgebildet werden kann, müssen Kontroll- und Datenflussabhängigkeiten aus dem Java Bytecode extrahiert und in ein Graphformat übersetzt werden. Dieses wird dann von einem Scheduler verwendet, um daraus die Konfiguration des CGRAs zu bestimmen.

Ziel dieser Arbeit ist die Implementierung eines neuen Graphgenerators, der zusätzlich auch schleifenübergreifende Abhängigkeiten (loop carried dependencies) aus dem Bytecode extrahieren kann. Zusätzlich müssen innere Schleifen erkannt werden. Für die Repräsentation des Graphen müssen die bestehenden Klassen um die neuen Informationen erweitert werden.

Student: Gregor Koch

Supervisor: Kris Heid

Time period: 10/07/2015 - 04/07/2016

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Es besteht bereits die Möglichkeit mehrere SpartanMC Kerne auf einem FPGA unter zu bringen und diese über sogenannte Core Connectoren kommunizieren zu lassen. Dabei hat jeder Kern des Systems seine eigene Firmware. Bei Multicore Anwendungen kann es jedoch sein, dass mehrere Kerne prinzipiell die selbe Firmware benötigen. Da der Speicherplatz bei vielen Prozessorkernen durchaus zur kritischen Ressource werden kann, ist es naheliegend einen globalen Firmwarespeicher für alle Kerne zu verwenden.

Ziel dieser Arbeit soll sein den SpartanMC Kern zu modifizieren, um Stalls zu unterstützen, welche hierfür benötigt werden. Ein zweiter Teil der Arbeit soll sich damit beschäftigen ein Memory Modul zu entwerfen und es mit einem Arbiter auszustatten, welcher den Zugriff auf den Speicher festlegt und jeden Kern mit einem Instruction Cache auszustatten.

Student: Steven Leduc

Supervisor: Kris Heid

Time period: 10/01/2015 - 04/01/2016

Am Fachgebiet Rechnersysteme (und an der Professur Mikrorechner der TU Dresden) wird ein SoC-Kit rund um den SpartanMC Soft-Core entwickelt. Dieser ist ein speziell für die Verwendung in FPGAs entwickelter CPU-Core. Aufgrund dieser Zielplattform nutzt der SpartanMC eine Befehls- und Datenbreite von 18 Bit, welche die Strukturen aktueller FPGAs optimal ausnutzt.

Ein Hauptaugenmerk bei der Weiterentwicklung des SpartanMC Toolkits liegt aktuell auf der Erweiterung der Multi-Core Fähigkeit des SpartanMC. Ziel ist es, Anwendungen für den SpartanMC zu finden, welche sich gut parallelisieren lassen. Eine Firewall ist potenziell eine solche Anwendung, die eine parallele Abarbeitung Paketen erlaubt.

Ziel dieser Arbeit soll es sein, eine eigene kleine Firewall App auf Basis des SpartanMC zu entwickeln oder eine Open Source Implementierung wie bspw. pfsense oder ipfire auf SpartanMC zu portieren. Der Fokus soll hierbei auf einer sinnvollen Aufteilung der Anwendung liegen, sodass zwischen den Prozessoren eine Art Pipeline entsteht. So wäre es denkbar, dass der erste Prozessor Pakete über die erste Ethernet Schnittstelle entgegen nimmt, diese an den ersten Kern weiterleitet, welcher einen Port Filter implementiert. Auf dem zweiten Kern findet eine IP-Adressen Filterung statt. Wurde das Paket bisher nicht verworfen, wird es an den letzten Kern weitergeleitet, der das Paket auf der Ausgangs Ethernet-Schnittstelle ausgibt.

Student: Jakob Wenzel

Supervisor: Christian Hochberger

Time period: 10/01/2015 - 03/31/2016

Das SpartanMC SoC-Kit ist eine Werkzeugkette und ein Satz von Soft- und Hardware-Komponenten, die dem Anwender erlauben, ein anwendungsspezifisches SoC zu konstruieren, ohne selbst Spezialist für FPGAs zu sein.

Bisher verwendet das SpartanMC SoC-Kit die Hersteller-Werkzeuge, um die FPGA-Konfiguration zu berechnen. Dies kann im Einzelfall leicht 15 Minuten und mehr benötigen.

Im Rahmen dieser Arbeit soll nach Möglichkeiten gesucht werden, mit Hilfe der RapidSmith Tools ein SoC erheblich schneller fertig zu stellen, als dies bisher möglich ist.

Project Seminars Bachelor

Student: Philipp Käsgen

Supervisor: Philip Gottschling

Time period: 12/01/2015 - 03/31/2016

Zur Überlagerung von zwei Datenflussgraphen werden sogenannte Kompatibilitätsgraphen erstellt, die angeben, welche Teile der beiden Graphen wiederverwendet werden können. In diesen wiederum muss anschließend der größte vollständig verbundene Teilgraph (Clique) gefunden werden. Für einen allgemeinen Graphen ist dieses Problem NP-Vollständig (Non-Polynomial). Für spezielle Arten von Graphen (Complete, Triangular, etc.) gibt es bereits Algorithmen, die das Maximum-Clique-Problem in polynomieller Zeit lösen.

Im Rahmen dieser Arbeit soll untersucht werden, inwiefern Kompatibilitätsgraphen, die aus Datenflussgraphen hervorgehen eine der besonderen Eigenschaften aufweisen.

Student: Melanie Braun

Supervisor: Kris Heid

Time period: 09/11/2015 - 02/03/2016

Um ein SoC zu konfigurieren, steht dem Nutzer momentan lediglich ein grafisches Interface zur Verfügung. Hier kann ausgewählt werden, welche Komponenten miteinander verknüpft werden oder auf welchen IO Pins die Peripherie agieren soll. Diese Methode der Konfiguration ist für Nutzer die genau wissen wie das System aussehen soll mit viel Aufwand verbunden. Aus diesem Grund wurde mit der Entwicklung eines Kommandozeilen-Tools bereits begonnen, welches die Möglichkeit bietet mit wenigen Kommandos Komponenten hinzuzufügen und zu verknüpfen.

Ziel dieser Arbeit ist konkret die Weiterentwicklung des Kommandozeilen-Tools um eine automatische Vervollständigung aller momentan möglichen Befehle, was eine Konfiguration noch weiter beschleunigt. Außerdem verwendet das Kommandozeilen-Tool eine abgeänderte Version der Backend Bibliothek als das grafisches Interface. Hier sollen beide Versionen angepasst werden, um ein konsistentes Backend anzubieten.