M.Sc. Leon Mayrhofer

Courses

Research Topics

Open theses

Supervisor: Leon Mayrhofer

Earliest start: sofort

Type: Bachelor Theses

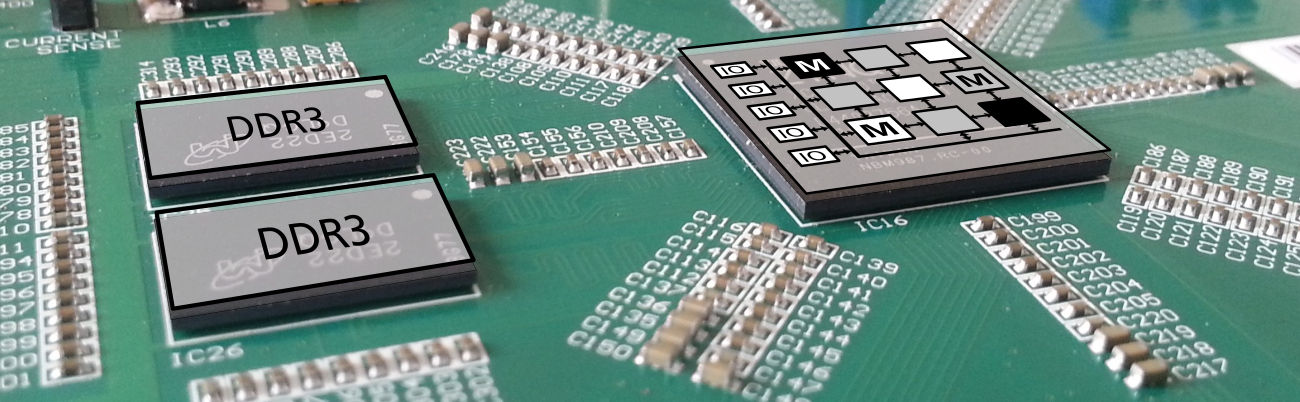

Das Fachgebiet Rechnersysteme betreibt das SpartanMC SoC-Kit, welches für den Einsatz auf FPGAs optimiert wurde. Ein Bestandteil des SoC-Kits ist der Peripherie-Bus und die dazugehörige umfangreiche Sammlung an Peripherie-Komponenten. Mit Hilfe von jConfig ist das automatisierte Erstellen von quasi arbiträren Kombinationen aus Peripherie-Komponenten in Verbindung mit SpartanMC soft-cores möglich. Neben den HDL Beschreibungen der Peripheriemodule werden unter anderem auch Hilfsdateien für die Compiler-Toolchain des SpartanMC erstellt.

Seit einiger Zeit wird parallel zu dem SpartanMC auch ein eigener RISC-V Kern in Chisel entwickelt. Dieser befindet sich aktuell jedoch in einem deutlich weniger ausgereiften Stadium. So gibt es für diesen Prozessor unter anderem noch keine Möglichkeit, Peripherie automatisiert und standardisiert zu erzeugen und in den Toolflow zu inkludieren.

Ziel dieser Arbeit ist es, eine Analyse des SpartanMC Peripheriesystems durchzuführen. Hierbei soll zuerst festgestellt werden, ob jConfig so angepasst werden kann, dass damit auch Konfigurationen für RISC-V Prozessoren inklusive der benötigten Hilfsdateien erstellt werden können. Außerdem soll eine Performance Analyse der einzelnen Peripherie-Komponenten durchgeführt werden. Dabei geht es vor allem um die maximal erreichbare Taktfrequenz.

Basierend auf den Erkenntnissen aus den zuvor ausgeführten Analysen soll ein Peripheriesystem für den RISC-V Prozessor erstellt werden. Dieses soll den maximal erreichbaren Takt des RISC-V Kerns nicht beeinflussen.